关键词:ISP器件,接口电路,VHDL,VXI总线

1 引 言

随着电子技术的飞速发展,ISP(In-SystemProgrammability)的出现代表着新一代PLD的方向,它消除了传统PLD的某些限制和弊病,提高了器件及板级的可测试性和系统的可靠性,提供了现场系统重构或现场系统用户化的可能性,使遥控现场升级及维护成为可能。基于此,采用ISP器件设计VXI接口电路是比较理想的选择。在本电路中我们选用了LatTIce公司的ISPLSI1032。ISPLSI1032的结构主要包括:

(1)全局布线区(GlobalRouTIng Pool)。该区位于芯片中央,它将所有片内逻辑联系在一起,它的各输入、输出之间的延迟是恒定和可预知的。

(2)万能逻辑模块(Generic Logic Block,GLB)。万能逻辑模块是该器件的基本逻辑单元,它由逻辑阵列、乘积项共享阵列、输出逻辑宏单元和控制逻辑组成。乘积项共享阵列将乘积项分配给或门,通过一个可编程的与/或/异或阵列的输出来控制该单元中的触发器,使乘积项共享比较灵活。每个输出逻辑宏单元有专用的触发器,每个触发器与其它可组态电路的连接类似GAL(Generic Array Logic)的OLMC(Output Logic Macro Cell),可以被组态为组合输出或寄存器输出。

(3)输出布线区(Output RouTIng Pool)。输出布线区是介于GLB(Generic Logic Block)和IOC(Input Output Cell)之间的可编程互连阵列,通过对该区的编程可以将任一个GLB输出灵活地送到I/O的某一个端口。

(4)输入输出单元(InputOutputCell)。该区引导输入、输出或双向信号与具体的I/O引脚相连接,形成输入、输出、三态输出的I/O口。

(5)巨块(Megblock)。巨块是GLB及其对应的ORP(Output RouTIng Pool)、IOC的总称。ISPLSI1032中有两个巨块,分布在全局布线区的两侧。每个巨块包含GLB、I/O口和专用输入端,专用输入端不经锁存器,直接输入在软件分配下供本巨块内的GLB使用。

外部信号通过I/O单元引导全局布线区,以完成任意I/O端到任意GLB的互连、任意GLB间互连以及各输入I/O信号到输出布线区的连接。器件的所有功能均可由一个GLB或多个GLB级联完成。

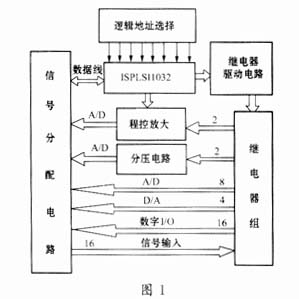

2 测试系统对接口电路的功能要求

接口电路是VXI系统资源到被测对象的信号通路,其作用在于控制信号的分配、转接和调理。主要功能包括:连接来自VXI模块的信号送往被测对象的电缆;部分VXI资源直接输出的通路转换和选择;对部分信号的预处理。3 VXI接口电路对ISP器件的要求VXI接口电路要求接口芯片严格遵守VXI总线的电子技术规范以及电磁兼容性规范等。它对ISP器件有以下具体要求:

(1)专用输入和I/O引脚能够监测并防止低于-1.5V电压的出现。

(2)每个I/O单元可独立编程为组合输入、寄存器输入、锁存输入、输出或带有三态控制的双向I/O引脚。

(3)接收逻辑高电平门限在2.0V以上,低电平门限在0.8V以下。

Lattice公司的ISPLSI1032器件是当今世界上速度较快、密度范围较广的器件,它的系统速度可达180MHz,可以相当于43750个PLD门。它具有最大的灵活性,硬件可以重新组态。它完全符合VXI总线的规范,可以满足VXI对接口器件的要求。

4 VXI接口电路的硬件连接

本文设计的接口电路原理如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)