当今复杂的雷达与航空电子系统要求高处理性能,但同时又面临着小尺寸、轻重量与低功耗 (SWaP) 限制。驱动这些系统的功能都属于信号处理密集型,因此高效实施在高性能低功耗小型处理器上执行的数字信号处理 (DSP) 算法,能够为它们带来极大的优势。此外,这些系统还具有不断提高的设计与数据使用需求。为了满足 SWaP 的效率与自适用性需求,可编程 DSP 与片上系统 (SoC) 现已成为处理平台理想选择。它们能以极低的功耗为雷达与航空电子设备,以及雷达与航空电子常配套的软件定义无线电 (SDR)、影像以及视频应用提供无与伦比的信号处理功能。

要满足对 SWaP 高效率 SoC 不断增长的需求并非易事。这要求既要低成本地提供高性能,又要达到低功耗目的,以实现工作与环保目标。德州仪器 (TI) 基于 KeyStone 的多内核器件是实现 SWaP 效率的关键。它们可为 TI 领先 TMS320C66x DSP 内核进行多内核实施,以小型封装提供每瓦最低功耗。KeyStone 器件以不同的性能提供,在整个系列产品中实现了软件兼容。这可满足多样化需求,在设计时为未来发展预留空间,实现高效开发。KeyStone 平台中的 TI TMS320C6657 与 TMS320C6655 器件是雷达与航空电子系统的理想选择。这些器件分别为引脚兼容型单内核与双内核 KeyStone DSP。

定点与浮点处理

使用多个数字信号处理器 (DSP) 内核是通过日益复杂的信号处理技术推动波形密集型应用发展的重要技术,可充分满足航空电子设备、雷达、声纳、信号智能 (SIGINT)、影像与视频处理以及软件定义无线电的需求。多内核功能将各种不断丰富的 AcceleraTIonPac 与面向多内核 DSP 的开发工具进行完美结合,能够以紧凑的封装在极低的单位功耗性能下实现高性能。

主要特性

AccelerationPac

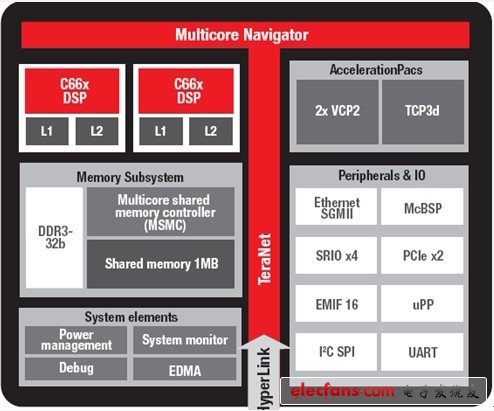

除优异的 DSP 性能外,C6657/55 还具有维特比及Turbo AccelerationPac,在充分利用每个内核 1MB L2 存储器与 1MB 共享存储器的同时,还可在低功耗硬件中处理通信与波形算法。这些 AccelerationPac 可独立于可编程内核运行,将 DSP 资源释放出来用于其它处理,从而可降低时延,优化软件开发。KeyStone 架构的多内核导航器提供一个基于硬件的抽象层,可将软件开发人员从底层硬件设计的具体繁琐工作中解放出来。多内核导航器的队列与描述符可用于自动将软件任务指向适当的资源,使可扩展性与资源池化成为处理器的整体功能。使用多内核导航器的软件可运行在任何 KeyStone 器件上,无需变更便可提供从一个 DSP 内核到多个 DSP 内核的可扩展性。这些因素综合在一起,可提供以 SWaP 为导向的应用所需的低功耗高性能。C6657/55 采用 40 纳米工艺技术,可在 1.25GHz 的频率下提供高达 80GMAC 和/或 40GFLOP 的性能。图 1 是 C6657 的功能图。

图1:TMS320C6657/55 方框图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)