摘 要 :为解决针对每一个CCD像素的高速采集和实时计算机处理的问题,本文提出一种利用增强型并行口(EPP)技术和可编程逻辑器件(CPLD)对CCD信号的每个像素进行高速采集的方法。着重介绍了EPP技术及CPLD技术,详细给出了针对CCD信号每一个像素进行高速采集的设计方案。

关键词 :增强型并行口(EPP);CPLD;CCD;FIFO

前言

CCD(Charge Coupled Device),即电荷耦合器件,是20世纪70年代初发展起来的新型的固体成像器件,CCD芯片借助于必要的光学系统和合适的外围驱动与处理电路,可以将景物图像,通过输入面空域上逐点的光电信号转换、存储和传输,在其输出端产生一时序视频信号,并经末端监视器同步显示出人眼可见的图像。随着CCD技术的迅猛发展,针对CCD信号的采集以及采集之后的信号如何与计算机进行信息通信,就成为CCD应用的一个重要问题,而能够针对CCD每一个像素进行高速采集并实时地传输给计算机处理,将会大大地提高采集到的CCD信号的精度并解决实时处理的问题。

EPP技术和CPLD技术

EPP技术(增强型并行接口技术)可以进行高速的双向数据传输,它可以区分两种类型的信息,并分别定义为数据和地址,而且它可以实现高速的方向转换,因此非常适合数据采集领域。EPP可以在一个ISA总线周期内完成包括握手联络在内的一字节的数据读写工作。数据线是双向的,一个控制信号负责确定数据端口的方向,另外两个控制信号则用来区分数据线上的数据和地址信息。EPP传输可以自动生成控制信号并检测对方的应答。EPP模式支持4种 *** 作,分别是地址写入、数据写入、地址读取及数据读取。数据读写一般用于主机与外设之间的数据传送,地址的读写一般用于地址、通道、命令和控制信息的传送。当EPP模式要写入一个数据字节,需要将数据写入EPP数据寄存器,写 *** 作将导致接口开启一个完整的数据写入周期。接口的硬件把待写入数据置于D0~D7,然后接口自动触发握手联络信号,并检测外设的应答。读取1字节和此类似,对EPP数据寄存器进行读 *** 作将引发一个完整的数据读写周期。地址的传输过程和数据的传输过程基本上一样。EPP的基地址通常是378h,接口使用的地址为378h~37fh。

CPLD(可编程逻辑器件)技术可以将数字电路集成到一块芯片上,大大减小了电路板的体积,而且它的可编程性使得设计好的电路在升级和修改上变得非常简单和方便。在采集系统中将使用以上两种技术并且结合A/D(模数转换器)和FIFO(先入先出缓存器)来设计,很好地解决了CCD信号的采集和处理难题。

系统的构成和基本原理

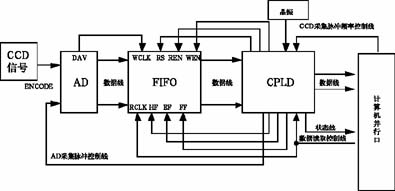

CCD信号采集系统由以下几个部分构成:CCD数字传感器、A/D、FIFO、CPLD、计算机,如图1所示。

当A/D接收到CCD信号并将CCD每一个像素点的电压值转换成12位精度的数字量,送入FIFO中,通过CPLD的逻辑控制解决FIFO和A/D之间的速度不匹配问题,并控制FIFO的数据传输给计算机并行口。

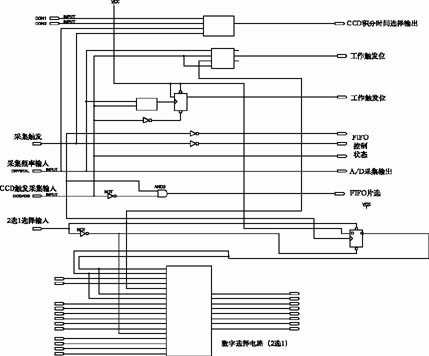

CPLD对整个采集系统进行控制,包括2选1数据选择电路、工作触发电路、CCD积分时间选择电路、FIFO工作状态控制电路,电路图如图2所示。当采集准备就绪,由CCD的采集使能脉冲对采集卡的各个芯片进行初始化,此后,由CCD的采集脉冲通过AD的ENCODE端向AD发出采集脉冲,当AD一次采集完成之后DAV发出高脉冲,此脉冲作为FIFO的写脉冲信号。同时采集脉冲也向数字比较器中的计数器发出计数脉冲,并行口同时检测采集脉冲和读取脉冲的数目,当读取脉冲的数目少于采集脉冲的数目时,并行口向FIFO中读取数据,这样既可以保证FIFO内不会残留有数据,也可以保证读写脉冲能以最短的时间结束,大大缩短了采集时间。一次采集完成之后,等待CCD发出下一次采集的指令。其中并行口向FIFO中读取数据时,每次数据将分成2次读取,每次读取总位数的一半,并加上高低识别位,以使数据读入计算机中后计算机能够分别识别高低位。

在采集系统中选择合适的芯片将使得采集系统的采集速度达到并行口的最大传输速度,精度最大可达14位。由于采集系统通过并行口与计算机进行通信,避免了计算机硬件电子器件对采集卡的电磁干扰,因此具有良好的抗干扰性。

采集系统的驱动程序

VC++对底层的 *** 作能力非常强大,可以方便地实现对并行口的读写及 *** 作,而且后期对采集的信号进行分析处理也非常方便,通过VC++封装动态链接库(DLL)作为采集系统的驱动程序,主要封装以下几个函数。

BOOL PASCAL EXPORT PTC_Open (PTC_HANDLE *phPTC);//打开并行口

void PASCAL EXPORT PTC_Close(PTC_HANDLE hPTC);//关闭并行口

BYTE PASCAL EXPORT PTC_Readdata (PTC_HANDLE hPTC);//读取并行口数据寄存器

void PASCAL EXPORT PTC_Writedata (PTC_HANDLE hPTC, BYTE data);//写并行口数据寄存器

BYTE PASCAL EXPORT PTC_Readstatus (PTC_HANDLE hPTC);//读取并行口状态寄存器

BYTE PASCAL EXPORT PTC_Readcontrol (PTC_HANDLE hPTC); //读取并行口控制寄存器

void PASCAL EXPORT PTC_Writecontrol (PTC_HANDLE hPTC, BYTE data);//写并行口控制寄存器

详细的代码由于篇幅关系不再一一列举了。

结束语

利用CCD信号的采集脉冲信号和数据输入信号的同步性,采集卡可以实现对CCD信号的每个像素进行采集,使得采集数据达到很高的精度,而且可以通过灵活地更改CPLD的主控电路来实现FIFO不同的读取方式,满足不同工作的要求。此外FIFO的速度和精度都非常高,可以通过更换高速、高精度的AD来达到更好的采集效果。最好通过并行口和计算机通信,避免了计算机内部电路对CCD信号的影响,也大大改善了采集的效果。

参考文献

1 Jan Axelson,那怡超译.并行端口大全.中国电力出版社. 2001

2 冯敏. Visual C++++.NET编程基础.清华大学出版社. 2002

3 潘松,王国栋.基于EDA技术的CPLD/FPGA应用前景.电子与自动化出版社. 1999

4 冯志辉.用计算机CPLD设计数字电子系统.新技术新工艺出版社. 2002

5 戴紫彬.在系统可编程器件的输入信号处理技术.电子技术出版社. 2000

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)