基于DSP的最小图像采集处理系统设计

采用TI公司的TMS320C6713,通过地址译码和总线隔离,直接将数字图像传感器芯片OV7620接入;利用EDMA独立传送的特点,在不增加DSP软件开销和对总线占用的情况下,实现视频图像的实时采集和处理。经过验证,系统具有实时性好、成本低、开发周期短的特点。通过总线隔离和数据锁存实现了DSP与低速LCD显示模块的接口。针对具体的硬件电路给出了驱动例程。

关键词 DSP嵌入式系统 图像采集 图像处理

引 言

在以DSP为核心的视频处理系统中,视频采集的方法通常可以分为两大类:自动的视频采集和基于DSP的视频采集。前者通常采用CPLD/FPGA控制视频解码芯片,通过FIFO或者双口RAM向DSP传送数据,特点是数据采集模块独立运行,占用DSP资源少,但实现相对复杂,成本偏高;后者通常由DSP控制视频解码芯片并同步各种时序,将视频数据读入。其特点是实现相对简单,成本有所降低,但对视频解码芯片的控制较为复杂,占用DSP处理时间。

如果通过适当的逻辑电路让数字图像传感器芯片直接接入DSP,则可省去视频控制解码芯片、CPLD/FPGA、FIFO或双口RAM,在不增加DSP软件开销的情况下,大大降低系统的复杂程度和成本,缩短开发周期。

1 硬件系统设计

1.1 系统总体结构

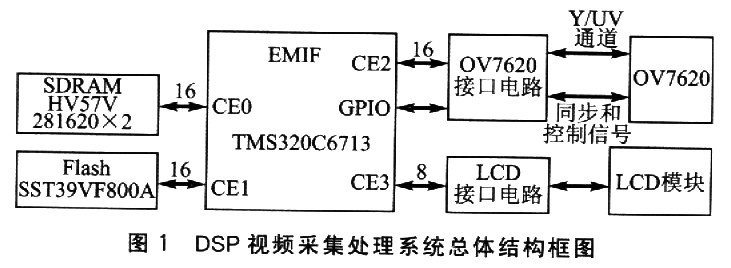

系统结构框图如图1所示。DSP采用TI公司发布的C6000系列高速浮点型信号处理器TMS320C6713,其峰值处理速度达l350 MFLOPS(百万次浮点每秒)。其外部存储器接口EMIF(External Memory Interface)包括4个CE空间,其中CE0被配置为16位同步空间,接SDRAM;CEl为16位异步空间,接Flash;CE2为16位异步空间,经过地址译码和总线缓冲将数字图像传感器OV7620接入;CE3为8位异步空间,经过数据锁存和总线隔离将LCD显示模块接入。

1.2 OV7620的配置和硬件连接

OV7620是OmniVision公司生产的CMOS彩色/黑白图像传感器,在本系统中被配置为16位逐行扫描QVGA方式,RGB原始数据输出,分辨率为320×240,SCCB总线,内部默认的行曝光方式;同时使能HREF信号对PCLK进行门控,即只有当HREF有效时像素时钟信号才被输出到PCLK引脚上,否则该引脚保持无效。这样EDMA可以始终处在使能状态,从而简化采集过程。

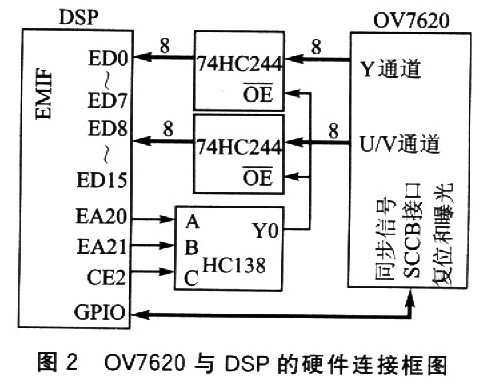

OV7620与DSP的硬件连接框图如图2所示。在对OV7620复位结束后,DSP通过GPIO模拟SCCB总线完成对OV7620内部功能寄存器的配置,之后数帧内图像数据和同步信号将逐渐稳定。Y通道和U/V通道在分别经过74HC244总线缓冲器之后接入EMIF低16位数据总线。CE2与地址线EA20、EA21经过译码产生2片74HC244的选通信号,此时OV7620的读地址为

0xA0000000。

1.3 EDMA数据采集

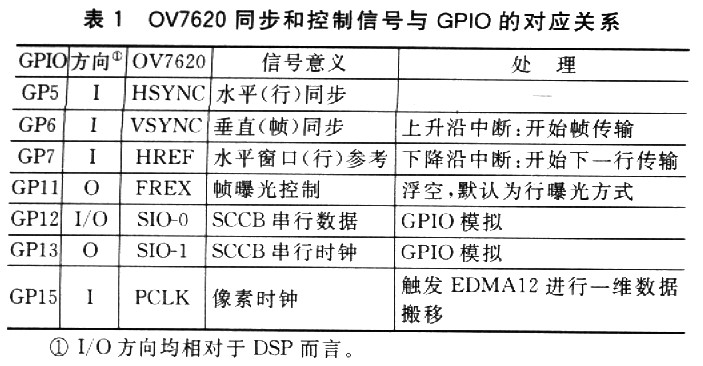

在16位逐行扫描方式中,图像的每行RGB原始数据均被OV7620先后输出两次,因此,只须读取其偶数次HREF信号对应的数据即可获得整个图像信息。这样可以减少图像采集所占用的存储空间和总线资源。OV7620同步和控制信号与GPIO的对应关系如表1所列。

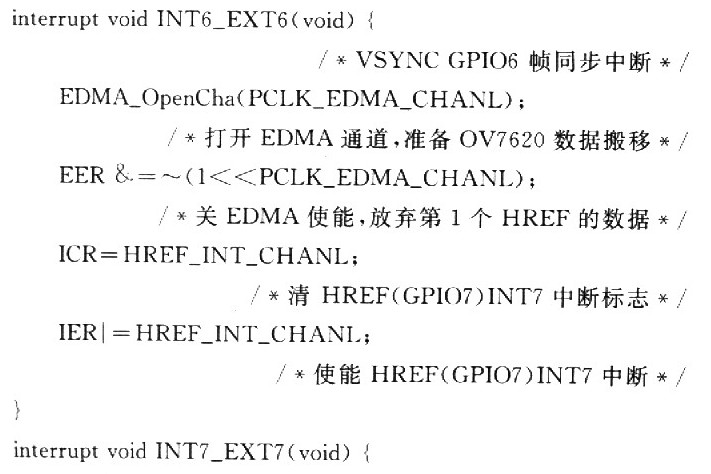

本系统采用EDMA的第12个通道(EDMAl2)进行图像数据采集。该通道被配置为16位一维传输方式,中断禁止,PCLK的上升沿触发EDMAl2搬移一个16位数据存入到SDRAM中,每次EDMA任务搬移一个HREF(320个16位)的图像数据。帧同步信号VSYNC上升沿触发DSP中断,对EDMA通道进行初始化,使能水平参考信号HREF中断并关闭EDMA通道(放弃第1个HREF、的数据),开始一帧的数据传输。HREF下降沿触发DSP产生中断,标志OV7620一次HREF数据输出的结束。如果接下来一次HREF数据需要被读入,则中断服务程序会对EDMAl2参数进行修正,使能EDMA12通道,开始下一行数据的传输;否则,就禁止EDMAl2,放弃下一次HREF数据。每接收1帧图像数据共产生240次HREF中断和120次EDMA数据传输。以下是OV7620数据采集的部分源代码:

1.4 LCD模块的驱动

采用液晶显示模块可以使图像处理结果实时显示出来,方便调试和演示,成本也较低。本系统选用北京宁和电子科技发展有限公司开发的NHC_34彩色液晶显示控制模块。该模块支持256色彩色显示,每个像素点用1个字节表示,分辨率为320×234;支持标准Intel 8位异步总线时序,有2页显示缓存,可任意设定显示页和 *** 作页。

LCD模块读写周期最短为350ns,而DSP外部总线接口时钟频率一般在100 MHz以上,即小于10ns。通过配置EMIF CE3空间控制寄存器CECTL3(地址为Ox01800014),可以将CE3空间的读写周期延长,与LCD模块无缝连接。但这样液晶模块的读写 *** 作会过长地占用系统总线,降低对其他存储空间(尤其是对SDRAM)的访问效率,进而影响系统的整体速度。

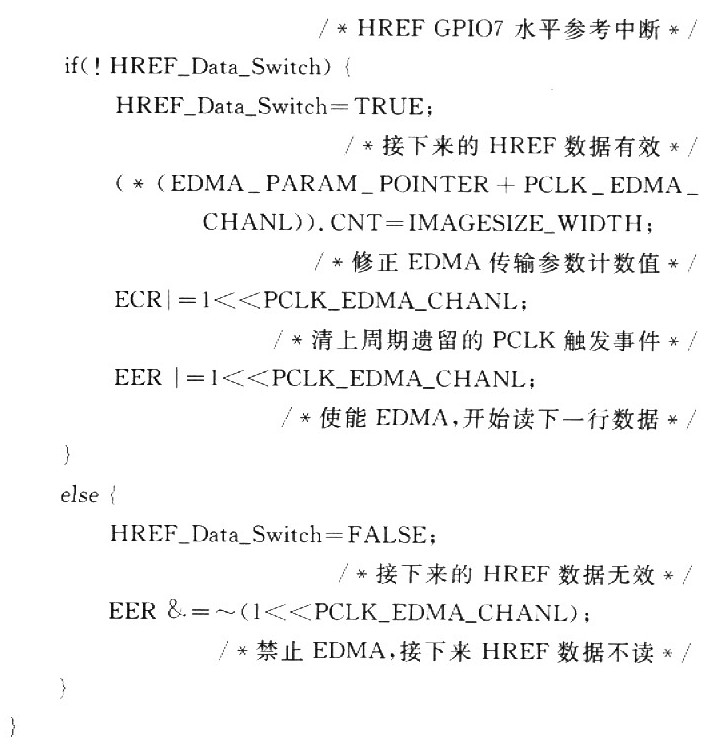

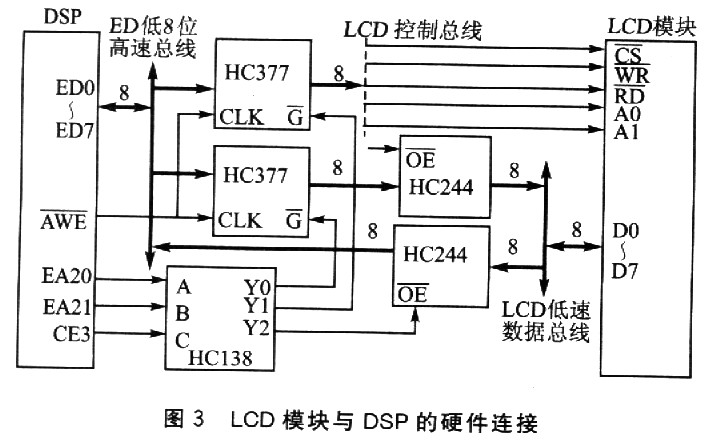

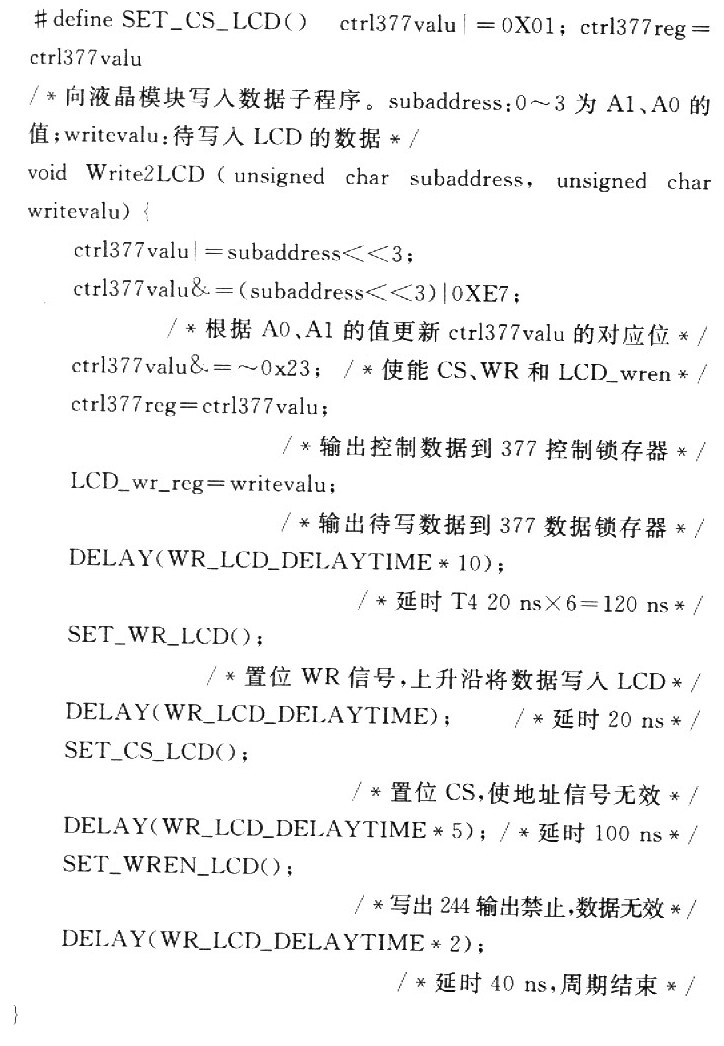

本系统采用了数据锁存和总线缓冲的方法,通过377锁存器模拟低速总线控制信号时序,利用244数据缓冲器对低速总线数据进行隔离。图3给出了DSP与LCD模块硬件连接图。系统有2片74HC377(简称为“377”),一片用来锁存模拟LCD模块的读写控制信号(控制377),另一片用来锁存写入数据(数据377),由异步写使能控制线AWE作为377的触发沿输入;CE3和EA20、EA21经过译码产生2个377的使能信号,DSP写数据377的地址为0xB0000000,写控制377的地址为0xB0040000。数据377的输出经一片总线缓冲器HC244(写出244,HC244简称为“244”)连接到LCD模块总线上,该244输出使能信号来自控制377。另有一片HC244(读入244)用来将LCD模块总线接到DSP低8位总线上,其输出使能信号同样由CE3和EA20、EA21经过译码产生,地址为0xB0080000,是DSP对LCD模块的读地址。

DSP根据LCD模块总线时序,通过定时器延时中断来间隔地写入数据到控制377,以模拟相应低速总线的控制信号,并适时从读入244读取数据(读周期),或者写入数据到数据377(写周期),就可以完成对LCD模块的读/写 *** 作。LCD写周期驱动例程如下(该程序通过延时来控制时间间隔):

2 软件系统设计

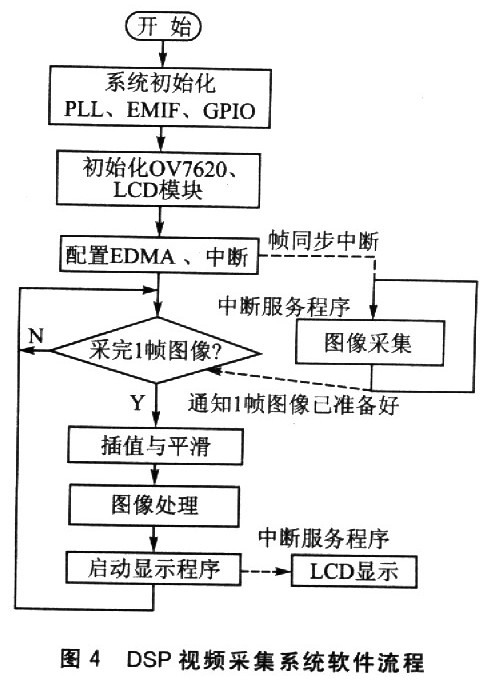

软件系统流程如图4所示。DSP在复位完成之后首先进行系统的初始化,配置锁相环、EMIF和GPIO,并硬件复位OV7620,通过GPIO模拟SCCB总线配置其内部功能寄存器,之后对LCD模块清屏。当EDMA没有被使能时,OV7620的同步信号仍能被EDMA事件寄存器捕获并保持,所以把EDMA的初始化放在OV7620和LCD模块的初始化之后,并在使能之前清事件标志。在中断被使能之后,OV7620的帧同步信号会触发系统中断,开始进行数据的循环采集,并在每帧数据采集完成之后置位相应标志,通知主程序进行处理。主程序在接到通知后对OV7620的原始数据进行插值和平滑,生成待处理的RGB24位色图像数据。图像处理和运算的结果被送到LCD模块进行动态显示,LCD的显示任务主要由中断服务程序完成,而此时主程序已开始等待和处理下一帧图像。

3 结论

本系统通过总线隔离和地址译码,只使用简单的逻辑芯片将OV7620接入DSP,并充分发挥EDMA独立传送的特点,仅占用DSP少量的软件开销和总线资源。就完成图像数据的采集。与采用视频接口芯片、外围FIFO和CPLD/FPGA等方案相比,很大程度上降低了系统成本,缩短了开发周期,而对系统总线的占用却并没有增加。利用数据锁存和总线缓冲实现了对LCD模块异步低速总线的接人;利用EDMA进行总线模拟,进一步降低DSP对LCD模块读/写的参与,减少系统中断次数,优化系统性能,能够将图像处理的结果实时和直观地显示出来。

与其他DSP嵌入式系统相比,本系统具有处理速度快、接口简单、成本低、能实时显示的特点,适用于视觉导航、视频实时处理等要求高速处理图像的场合,以及有实时演示要求的场合。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)