基于模型的DDS芯片设计与实现

0 引言

1971 年,美国学者J.TIerncy.C.M.Rader 和B. Gold 应用全数字技术,从相位概念出 发给出了直接合成波形的一种新的频率合成原理, 这就是DDS ( Direct DIGITAL Synthesizer),直接数字合成技术。近几年超高速数字电路的发展尤其是大规模超高速FPGA 技术日渐成熟,以及对DDS 的深入研究,使得DDS 的最高工作频率以及噪声性能已接近并达 到与锁相频率合成器相当的水平[1]。与其它频率合成方法相比,DDS 具有频率转换时间短、 频率分辨率高、输出相位连续、可编程、全数字化、易于集成等突出优点。本文提出的方法 基于Xilinx 公司和它的合作者联合提出的XtremeDSP 解决方案,从系统结构设计直接映射 到基于FPGA 的DSP 系统硬件实现。在这种基于模型的设计技术中,利用Simulink 的图形化界面由系统的技术条件建立系统的数学模型,通过算法对模型进行仿真优化,再转化成IP 核实现。System generator 同Simulink 模型工具结合,可以将算法参数化、最优化,并可 自动从行为级的系统模型转换到FPGA 实现,不需手工重设,从而避免了繁琐的编程工作,大大节省了开发时间并降低了出错的概率。

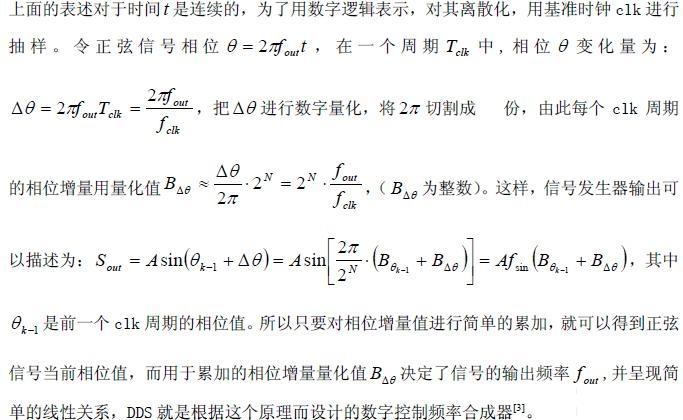

1 DDS 的基本原理

2 在MATLAB 中建立的DDS 模型并在ISE 中实现

2.1 建立DDS 模型

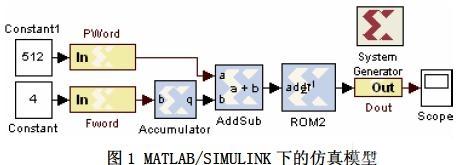

Simulink 是一个可用于多领域动态系统仿真的平台,为动态系统提供建模和分析的方法,提供交互的图形化方框图环境带有为信号处理、通信和控制等可定制的模块集。System Generator 就是Xilinx 公司的一个专有模块集(Blockset),它是Simulink 的一个插件, 包括基本DSP 函数和逻辑算符,其中包含的预先定义好的模块可以保证FPGA 实现时位和周 期的正确。用它可以自动生成VHDL 语言、测试向量等文件,还可以自动将特定的设计模块 映射成高度优化的IP 核模型。在本文介绍的设计中,最后生成的工程文件中就自动映射出一个累加器核和一个单口块ROM 核。

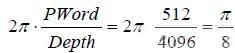

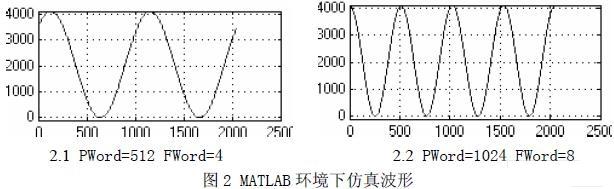

根据DDS 控制原理在MATLAB 环境中建立如下的模型(图1):其中在存储正弦数据的RO中设定Depth 为:4096,IniTIal Value Vector 为:2047*sin(pi*(0:4095)/2048)+2047, 即让System Generator 在编译过程中自动产生一个存储4096 个正弦数据的ROM。为了配合 使用开发板上的D/A 模块,ROM 中的每个值设置成12 位无符号数。Accumulator 模块用来进 行相位的累加,AddSub 模块将相位偏移量与相位累加值相加,作为ROM2 的地址输入。在仿真前,设置相位控制字为PWord=512,由公式算出移相后的波形应该较基准正弦波偏移 ;设置频率控制字FWord=4,将仿真时间设置为2048,这样 从理论上我们应该可以看到两个周期的完整波形输出。运行仿真,可以在Scope 中观察到如图2.1 中波形。改变控制字的值,就可以得到不同频率、不同相位的波形(图2.2)。

;设置频率控制字FWord=4,将仿真时间设置为2048,这样 从理论上我们应该可以看到两个周期的完整波形输出。运行仿真,可以在Scope 中观察到如图2.1 中波形。改变控制字的值,就可以得到不同频率、不同相位的波形(图2.2)。

2.2 在ISE 中实现并仿真

点击System Generator 图标中的generate 按钮,生成可综合的VHDL 代码,并在ISE 中打开。先对代码使用Synthesize-XST 进行综合,通过之后可以观察到系统RTL 级视图。 然后创建一个.tbw 文件对综合后的设计进行仿真,能够得到和MATLAB 环境下一样的仿真结果(按照正弦规律变化的离散数值序列)。为了能够在实验板上实现设计,在ISE 环境中建立 顶层文件,将System Generator 产生的文件与PicoBlaze 的控制程序文件结合,再进行对 应的功能仿真,正确后加载约束文件,生成比特流文件。

3 设计的硬件实现

选择在Xilinx 公司的Spartan-3E Starter Kit 开发板上实现整个设计。在该开发板 上,有一片LTC2* D/A 芯片,通过一个SPI 接口与FPGA 管脚相接,能够提供4 路独立的模拟量输出。为了便于对D/A 芯片以及各种控制接口的控制,在实现过程中使用了一个 PicoBlaze 软核。

PicoBlaze 是一个紧凑型、资源占用极少、完全嵌入式的8 位精简指令集 微控制器软核。我们可以在文本编辑环境下根据PicoBlaze 的指令系统编写自己的控制代 码,然后保存为.psm 格式的文件,再用Xilinx 的KCPSM3 assembler 对文件进行编译,编译通过后自动生成一个储存用户程序的ROM(VHDL 文件)。将生成的ROM 文件和KCPSM3 软核加载到工程中,并建立上层文件对各输入、输出口及中断进行配置,这样,一个PicoBlaze 软核就设计成功了。 在PicoBlaze 的控制程序中采用软件中断方式控制D/A 芯片以20KHZ 的频率对数字量采 样。在每个采样过程中,由PicoBlaze 软核控制向D/A 芯片发送32 位控制字,其中有12 位待转换的数字量、4 位通道选择控制字、4 位模式控制字,其余各位为0。在ISE 中对主时钟进行软件分频,将开发板上原本50MHZ 的时钟降低到100KHZ 之后再接到DDS 产生电路 的输入时钟端口。这样, 在FWord = 4的情况下, DDS 的输出频率输入时钟可以直接接入50MHZ 的晶振,这样,在同样频率控制字的情况下输出频率也会相应 提高。这里分频只是为了配合相对低速的D/A 芯片,以使得输出波形每个周期的采样数相对 多一些,以便于用示波器进行观察。

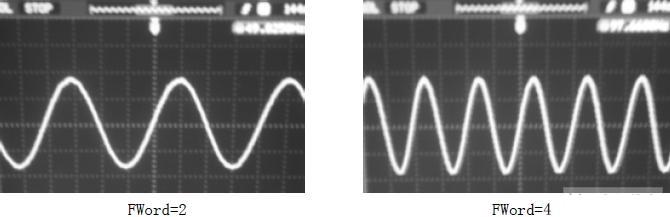

将生成的比特流代码下载到目标板,板上的开关信号作为用户接口控制FWord 的值,控制不同开关的关闭和开启,模拟不同频率控制字的情况,得到不同频率的波形,用示波器 观察开发板上J5 连接器的A 通道,得到如图3 的波形:观察波形,与由公式计算出的理论值吻合,证明了本文所介绍的方法的有效性、可行性。在ISE 的设计使用摘要窗口中,我们可以清楚的看到该系统所占用的芯片资源极少,由此可见,如果我们加大ROM 的深度,并且 通过DCM 时钟管理提高主时钟频率的话,能够很容易的实现更高频率、更高精度的DDS 芯片。

4 结语

该设计过程演示了在 MATLAB/Simulink 环境下使用Xilinx 公司的System Generator 模块集对DDS 建模,并在ISE 中进行编译、仿真,最终在开发板上实现DDS 功能芯片的过程。 虽然在ISE 集成环境中已经提供了DDS 的IP 核供编程者使用,但是只能产生正弦或者余弦 波形,在需要产生其它波形(如方波、三角波等)的场合难以发挥作用,而且根据DDS 原理使用软件编程方法产生其它波形具有一定的复杂性,容易出错且效率不高。本文介绍的方法 具有数字频率合成的普遍性,设计者通过修改ROM 中存储的初始值向量,可以用类似的方法 达到产生任意波形的目的。这是一种在Xtreme 系统中实现DSP 设计的普遍方法,使用这样的设计流程,可以避免编写烦琐的HDL 程序,更可以实现其它更加复杂的DSP 算法。该方法 充分发挥了使用FPGA 实现DSP 系统所具有的高度并行性、重构灵活性以及低性价比的优势, 在无线基站、复杂网络系统、视频服务和医疗图象等DSP 领域将得到更加广泛的应用。

本文的创新点:不仅提出了一种先进的基于模型的DDS 芯片的设计新方法,而且通过实 际实验在硬件开发板上实现了整个设计构想,实验结果符合设计要求,验证了该设计方法的 正确性、可行性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)