基于FPGA的次声波合成的电路设计

摘要:次声波是频率在10一~20Hz的波,在生物医学、气象学、军事等领域有着广泛应用前景,此频段的信号无法通过天线直接发射。应用DDS原理产生2路相干超声波,在空间干涉产生次声波。主要完成了基于FPGA的DDS电路设计,并且完成了系统软、硬件设计,通过Max+Plus11和Matlab的仿真表明该设计的原理正确、方案可行。

关键词:次声波;FPGA;DDS

次声波是频率在10-6~20 Hz之间的机械纵波。利用2个频率不同的超声波(频率通常在2×104~5×108Hz范围之间)在空间干涉组合可以形成次声波。

目前,大多使用直接数字频率合成(DDS)方法产生高频波形。本文利用DDS原理,通过FPGA产生2个不同频率的高频信号,再经过换能器转换成2路超声波,在外部干涉合成次声波。

1 DDS的基本原理和结构框图

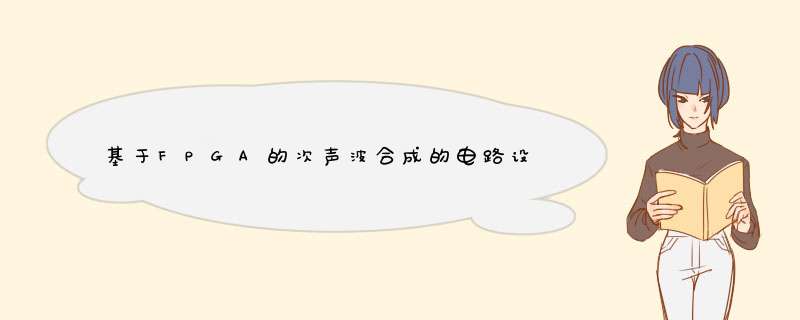

DDS(Direct Digital Synthesis)是从相位概念出发,将数字信号转换成模拟信号来获得所需波形的一种频率合成技术。日前,使用最广泛的是基于查找表(Look-Up-Table)结构的方法。图1是DDS的基本原理图。

DDS是由相位累加器(一个累加器、相位寄存器和加法器构成)、LUT(正弦查找表)、DAC(数/模转换器)和LPF(低通滤波器)组成。该DDS系统的核心是相位累加器。

假设频率控制字是M,相位累加器的长度为N。工作原理:每来一个时钟fc,N位的相位寄存器以步长M增加。相位寄存器的输出与相位控制字相加,然后输入到正弦查询表地址上。正弦查询表包含一个周期正弦波的数字幅度信息,每个地址对应正弦波中0°~360°范围的一个相位点。正弦查询表把输入的地址相位信息映射成正弦波幅度信号,驱动DAC,输出模拟量。相位寄存器每经过2N/M个fc时钟后回到初始状态,相应地正弦查询表经过一个循环回到起始位置。整个DDS系统输出一个正弦波。

输出频率:fo=fcM/2N;

最小分辨率:△fmin=fc/2N。

由上面的公式可知,输出频率由频率控制字M、相位累加器的长度N、时钟fc决定。

由于DDS的输出最大频率受奈奎斯特抽样定理的限制,所以fmax=fc/2。

2 次声波合成基本原理

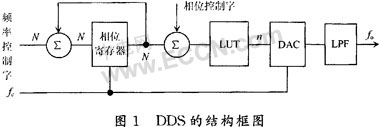

次声波的合成主要需要产生两个同相、频率差小于20 Hz的高频正弦波。

本文中,次声波合成的基本框图可由两个DDS基本框图构成。生成的高频信号f0,f1通过外部换能器转换成频率差小于20 Hz的超声波,经过干涉合成次声波。如图2所示。

3 用FPGA实现次声波的合成

3.1 FPGA的内部结构

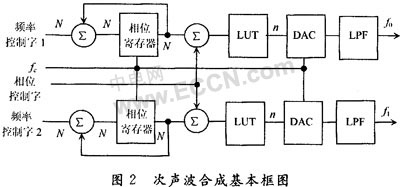

利用FPGA设计次声波的合成电路,可以把波形信息存储在ROM中,通过修改ROM中的波形数据来实现灵活的频率和相位要求。

本文中,利用LPM(参数化模块库),通过设置LPM模块的参数,来满足设计要求。图3是调用LPM模块设计的生成双路高频信号的核心电路。此电路由4个加法器(LPM-ADD-SUB),2个寄存器(LPM-DFF)及2个ROM(LPM-ROM)组成。F1[N..0],F2[N..0]为双路高频信号的频率输入控制字,CLK为同步时钟,T1[M..0],T2[M..0]为输出,可以接到D/A转换器上。由于本设计不需要相位调制,所以没有使用相位输入控制字。

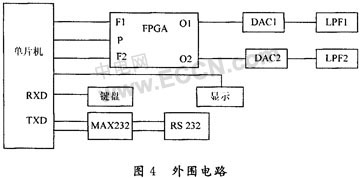

3.2 外围电路控制

图4为FPGA的外部控制电路。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)