FPGA在智能仪表中的应用

随着微电子技术的发展,采用现场可编程门阵列(FPGA)进行数字信号处理得到了飞速发展。由于FPGA具有现场可编程的特点,可以实现专用集成电路,因此越来越受到硬件电路设计工程师们的青睐。

目前,在自动化监测与控制仪器和装置中,大多以8位或16位MCU为核心部件。然而伴随着生产技术的进步和发展,对监测与控制的要求也在不断提高,面对日益复杂的监测对象和控制算法,传统的MCU往往不堪重负。把FPGA运用到这些仪表和设备中,可以减少这些仪器、设备的开发周期,大幅度提升这些仪器的性能,减少总成本和体积。

在低阻值、高精度线圈电阻测试仪中关键部分用FPGA硬件电路来实现,可以节省系统的面积开销、减少所用的芯片数和PCB板块数,提升系统性能,并降低成本。

低阻值、高精度测试仪系统结构介绍

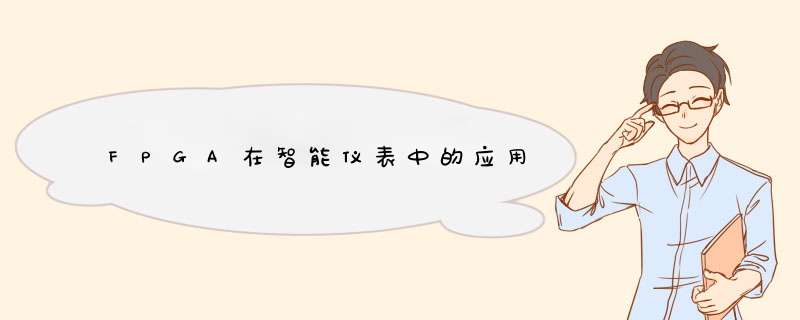

系统的待测体是一个绕有三组铜线圈的机构,外形尺寸大约是7×7×6(mm),外形结构较复杂。由于系统要通过测量待测线圈的阻值,来确定线圈的圈数,因此,要求有比较高的测量精度。按照工厂流水线作业的要求,待测体电阻值均在5Q以下,测量精度在±0.01Ω以内,反应速度在0.8s以内。整个测试系统由数据采样模块、数据处理模块和显示输出模块组成,系统的原理框图如图1所示。

数据采样部分

由于本系统要对微小电阻进行精确测量,因此采用四引线制测量法,配以高精度、低温漂的恒流源。本系统的A/D转换芯片采用Intersil公司的三位半A/I)转换器ICL7107,恒流源产生的10mA电流流经待测线圈,产生一个与线圈阻值成正比的压降。此压降通过三位半A/D转换器直接转换为七段码形式的十进制数据流,直接送至显示输出部分,由LED数码管显示输出。

数据处理部分

这部分有三个功能:

(1)将A/D转换器输出的七段码形式的数据转换为BCD码;

(2)将转换好的的BCD码数据进行相减,实现电阻值求差功能;

(3)将转换好的BCD码数据与设定的上下限进行比较,第2步得到的电阻差值与基准比较值进行比较,实现比较功能。

本文着重介绍这一部分的原理以及实现。针对数据处理部分,这一部分功能可以采用三种方案来实现:

(1)采用ALU和7485系列芯片来实现,这种方案需要6个ALU单元(3片处理4位BCD减法的单元和3片处理借位的单元)和18片74LS85芯片(作为数字比较器),占用相当大的系统面积,并且看起来非常繁琐功能复杂,不直观。时间延迟大,测量误差也比较大。

(2)完全采用数字组合逻辑电路来实现,这一方案设计门槛比较低,但是占用的系统面积、功耗和测量误差比第一种方案大的多,达到较难以实现的地步。

(3)采用FPGA来实现,把本部分要实现的功能完全集成在一块FPGA上,与上述两个方案比较,大大节省面积,系统功能让人一目了然,而且仪器稳准度更高,反应速度更快

显示输出部分

该部分有LED显示灯(红、绿)和LED数码管组成,根据输入显示相应结果。

FPGA实现的数据处理功能

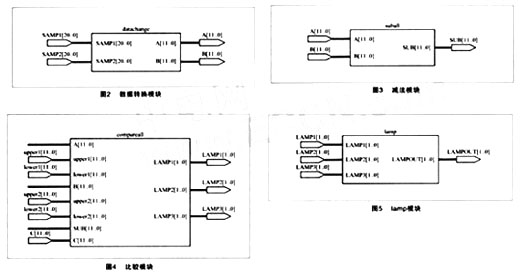

测试仪中通过待测线圈的压降通过三位半A/I)转换器ICL7107后,一输出的数据(samplel、sample2)均为七段码形式的十进制三位数(个、十、百位),要求与两个可调的上下限(BCD码拨码输入)进行比较,若在比较限度内则亮绿灯(greenl、green2),否则亮红灯(rerll、red2)。另外,两个采样值相减,若其差值(sub)在固定范围以内则亮绿灯(green3),否则亮红灯(red3)。所有的绿灯亮,总控的绿灯(greerl)才亮,否则,总控红灯(red)亮。设计方案按照TOP—DOwN的思想对系统进行整体功能划分,再以BOTTOM—uP方式进行设计输入,使系统具有层次感(hierarchy),各个功能模块内包含小的模块,也便于模块的重复调用,最后进行芯片的功能、性能等各项模拟。各模块功能及结构图介绍如下:

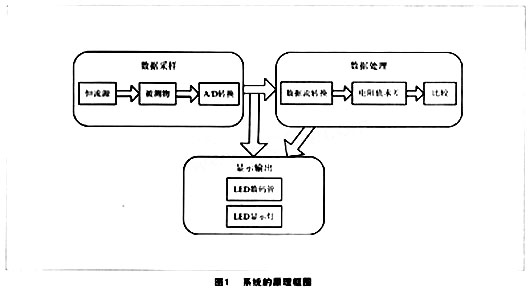

datachange(数据转换)模块

将输人为七段码的数据转换为BcD码,输出转换后的数据,直接送到显示输出部分,在LED数码管上显示出来,如图2所示。

suball(减法)模块

系统数据处理的核心部分,包括3个子模块,来实现采样的两个12位BCD码数之间的相减。其中的核心子模块为4位BcD减法模块,通过借位,将此模块串接,实现模块复用。将差值送到显示输出部分,在LED数码管上显示出来,如图3所示。

compareall(比较)模块

实现转换后数据(A、B)同设定的上下限(图中为upperl、lower。1和upper2、lower2)进行比较;减法模块得出的差值(sub),与设定的基准值c进行比较。最后输出比较结果,将结果送到显示输出部分,以LED显示灯形式来显示结果,如图4所示。

lamp模块

总控显示灯选择模块,根据输入的结果来决定输出灯的颜色,如图5所示。

具体算法流程如图6所示。

仿真验证

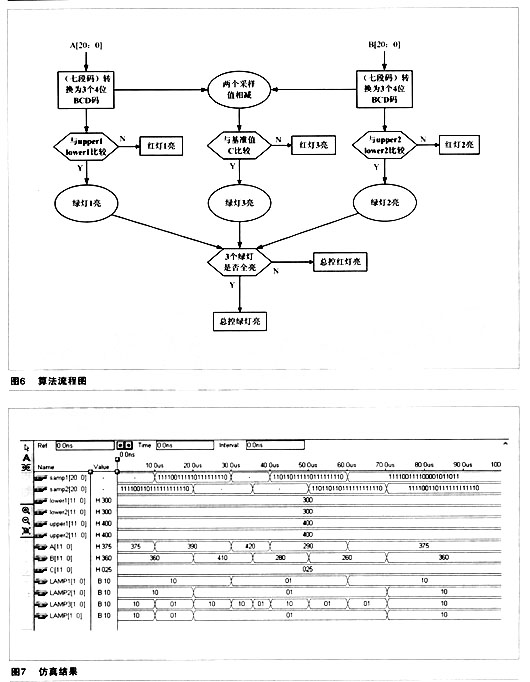

数据处理模块采用verilog语言编写,用Maxplus II进行功能仿真,设定upperl与upperl2值均为400(即上限4.0Ω),lowerl与lower2值均为300(即下限3.0Ω),基准比较值C为025(即电阻差值最大限度为0.25),采用六组不同区间数据作为采样输入,仿真结果如图7所示。

波形显示该算法完全正确,功能达到设计要求。我们采用Altera公司Cyclone系列的EPlC3芯片,进行FPGA仿真,并将其应用于实际系统中,完全达到预期效果。为了检验系统的精确度,采用精密数字微欧计进行校验,该仪表测量准确度达0.1%,分辨率最高可达1mΩ。

本文提出的设计方法,从实际应用来看,节省了面积开销,仪器稳准度更高,反应速度更快,并且降低了系统整体电路的复杂度,提高了系统集成度。经软件仿真和实际功能验证.证明设计可靠、设计方案可行,在实际应用中有较大的实用价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)