作者:Marian Hryntsiv, Dialog半导体公司(瑞萨全资子公司)文档工程师

简介

很多应用在其用户控制界面中采用机械电位计。我们可以将这些机械电位计换成更新且可靠的编码器控制元件和数字变阻器,它们是改变信号电气参数的组件。

本文中,我们使用了GreenPAK™ SLG47004。它是该项目的绝佳选择,因为其电路结合了两个数字变阻器和可配置逻辑来处理编码器信息。这种组合可实现许多设计:稳压电源、具有可调增益的放大器等。此外,数字逻辑可确定编码器的旋转速度。这种方法如图1所示。

图1

1. 系统概述

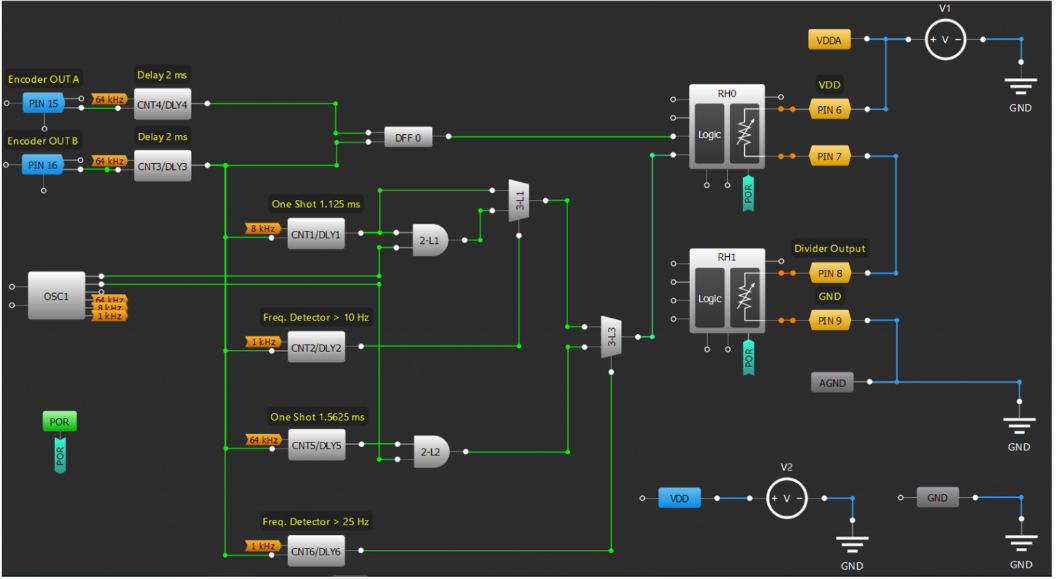

图2显示了基于SLG47004的内部电路设计。

图2:GreenPAK Designer项目

在基于GUI的免费软件GreenPAK Designer中创建的完整设计文件可从以下链接下载。

https://www.dialog-semiconductor.com/sites/default/files/2021-08/AN-CM-320_PotenTIometer_Controlled_by_an_Encoder.zip

增量编码器产生A和B输出信号,用于改变数字变阻器的电阻。变阻器形成电位计,并实现可调分压器来调节输出电压。

在任何时候,A和B信号之间的相位差为正或负,取决于编码器的运动方向。

速度由频率检测器、One-Shots和多路复用器构成。

本文中,我们使用了EC11编码器。由于开关切换抖动,编码器会产生嘈杂的输出振荡。为了消除这种噪音,我们采用了2毫秒的延迟。请注意,此延迟针对EC11编码器进行了调整(根据其数据表)。对于其他编码器,应该相应地评估延迟值。

2. 功能块架构

2.1. 数字逻辑说明

2.1.1. 确定编码器方向

首先,延迟宏单元将编码器输出信号的两个边沿延迟2毫秒。延迟宏单元起到抗尖峰脉冲滤波器的作用,可消除开关切换抖动。滤波后的信号B出现在One-Shots和频率检测器的宏单元输入端子,以及DFF的CLK输入端子上。滤波后的信号A出现在DFF的D输入端子上。当编码器码盘顺时针方向旋转时,信号A超前信号B,DFF输出为高电平;当编码器码盘逆时针方向旋转时信号B超前信号A,DFF输出低电平。所以DFF可以判断旋转的方向。变阻器上升/下降控制端子上的高或低信号决定了内部计数器对于CLK输入端子上的每个脉冲是进行增加计数还是减少计数。

编码器顺时针旋转的时序图如图3所示,编码器逆时针旋转的时序图如图4所示。

图3:编码器顺时针旋转的时序图

图4:编码器逆时针旋转的时序图

2.1.1.确定编码器速度

SLG47004具有10-bit数字变阻器,从而允许实施1024个调节步骤。可调分压器有3种调节模式。用户可以用step = 1个数字代码(模式1)、step = 10个数字代码(模式2)和step = 100个数字代码(模式3)共三种不同的步长来改变输出信号。采用了2个频率检测器以实现3种模式。第一种模式用来平滑准确地调整输出信号。当用户用小于10 Hz的频率调整旋钮时,会激活第一种模式。当频率在大于10 Hz小于25 Hz时激活第二种模式。频率大于25 Hz时激活第三种模式。

One-Shots为所需的脉冲数设置时间间隔。

根据频率检测器的输出,来决定数字多路复用器传递到变阻器的CLK输入端的脉冲数量是1个、10个或100个脉冲。

2.1.2. 每转的制动和脉冲数

该项目中使用了具有不同脉冲数和制动(位置)/阻尼点的编码器。对于15个脉冲,每个完整脉冲有两个制动/阻尼点。这意味着对于旋转编码器中的每个脉冲(或周期),都有两个制动/阻尼点:脉冲的上升沿(一次变化)和脉冲的下降沿(另一次变化)。如果您的旋转编码器每个脉冲有一个制动/阻尼点,那么每个脉冲有两次变化。对于这种类型的编码器,设计保持不变,除了频率检测器和One-Shots设置。他们的设置中,Edge Select应设置为“Falling”或“Rising”。在脉冲数和制动数不匹配的编码器中,Edge Select应设置为“Both”。

2.2. 电位计模式

对于此设计,我们使用了数字变阻器的电位计模式。该模式允许将两个2引脚变阻器组合配置为一个3引脚电位计一样来工作。当此模式启用时(寄存器 [917] = 1),用户只需要更改RH0内部计数器的值即可。在这种模式下,RH1计数器的值是电位计总计数值(1023)减去RH0计数器值后所得的数值。请注意RH0_B引脚和RH1_A引脚必须外部短接在一起。

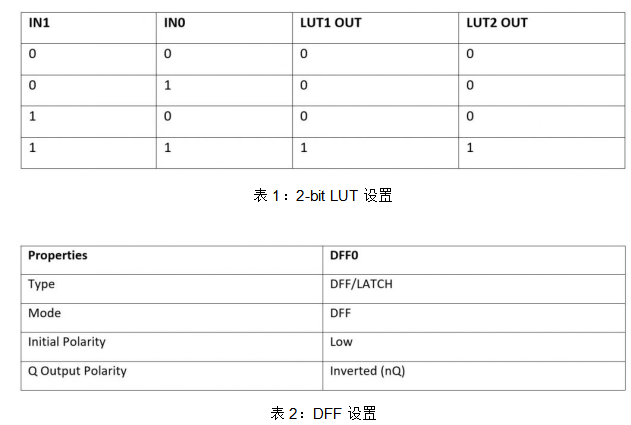

2.3. 宏单元设置

下表显示了3-bit LUT1和3-bit LUT3设置:标准逻辑门–多路复用器。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)