一、什么是5G

5G是第五代移动通信技术(5th-GeneraTIon)的简称,是新一代的蜂窝移动通信技术,也是继4G、3G、2G系统之后的延伸,5G的性能目标是高数据速率、减少延迟、节少能源、降低成本、提高系统容量和大规模设备链接。

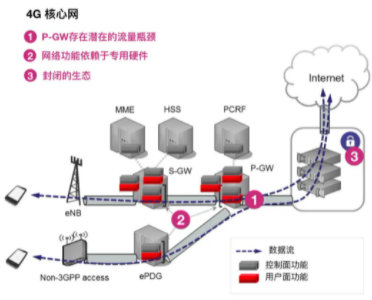

二、4G与5G核心网的区别

面向5G时代,预计随着流量陡增,4G核心网架构存在如下局限:

1)PGW存在潜在的流量瓶颈

在4G网络中,所有的数据面(用户面)流量都通过P-GW,这种集中式的架构尽管便于管理和维护,但受限于网络回传流量。

2)网络功能依赖于专用硬件

3)封闭的生态

为此,需对5G核心网架构进行重新设计:

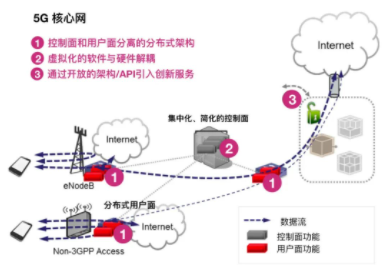

1)控制面和用户面分离的分布式架构

分布式的用户面可解决海量数据流量带来的瓶颈,同时,集中化、简化的控制面可增强网络管理能力。2)虚拟化的软件与硬件解耦

3)通过开放的架构/API引入创新服务

三、5G应用对时钟的要求

从4G到5G,与之前的技术迭代升级都大不相同。当然从4G到5G也不仅仅只是上网速度更快了这么简单。借用苹果的一句话说,那就是“Not than Faster”. 正是有了5G的出现,万物互联、工业4.0等才有望实现,这个世界也将真真正正的被改变。

但由于5G使用了频率更高,相应的波长也就更短的毫米波技术。速度是大大的提升了,但由于毫米波的覆盖距离更短,所以需要10倍以上的网络设备数量才能达到与之前4G相同的覆盖水平。

5G技术有如下三个因素,导致了我们对10倍以上的网络设备的需求:

1、更高的带宽:5G网络使用大量的MIMO和400G光传输技术,以支持10倍的移动下载速度及10000倍的流量。

2、云端:5G在基于云的基础设施(如:运营商级的以太网)上响应,以连接所有的设备,实现最大的带宽效率。

3、高密度:5G设备要部署在离最终用户更近的地方,所以会导致大量的设备被投放在不确定的环境因素中,如路边、屋顶、地下室、路灯、体育场、写字楼等地方。

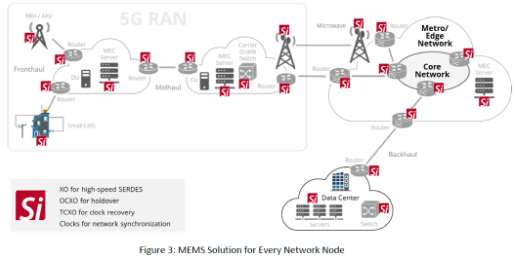

如上因素,导致了5G网络对时钟的要求也比4G严格10倍以上。

5G的云化,需要端到端是时间精度控制在130ns的级别,以保证基础设施的5G连接。这个要求不仅比4G的1500ns精度严格10倍以上,而且要求使用符合IEEE 1588的精准时钟协议的时钟器件,如时钟同步器件、高精度TCXO(温补振荡器)和OCXO(恒温振荡器)产品。

除了时钟同步解决方案之外,5G还需要极低噪声和低抖动的时钟器件,以支持400G 光模块和Massive MIMO设备。

四、“Cascade”系列产品的优势

SiTIme可提供完整的MEMS时钟解决方案,包括低抖动单端及差分振荡器、高精度TCXO、OCXO产品、时钟发生器、抖动消除时钟器件、同步时钟等相关产品。这些MEMS时钟解决方案相较于传统的石英器件,在对应使用环境的气流变化、温度变化、高温、振动以及电源的不稳定性带来的频率不稳定性,具有10倍优于石英产品的特性。

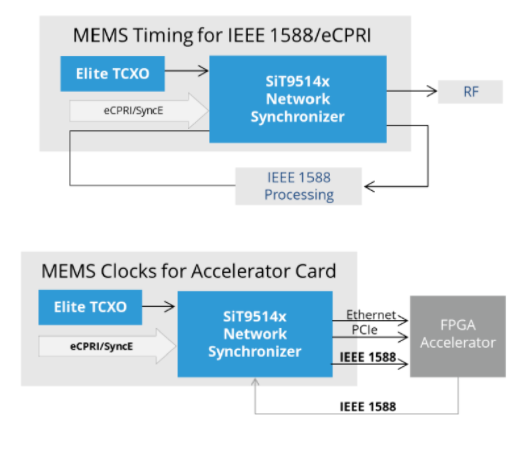

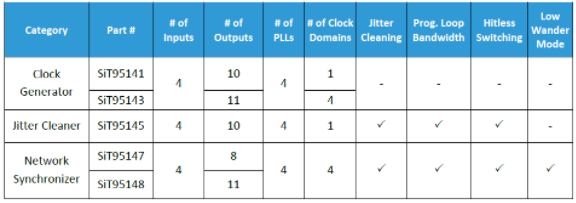

SiTIme的“Cascade”系列产品包括时钟发生器、抖动消除器件、时钟同步产品等系列,可独立或与SITIME的Elite TCXO/OCXO、 MEMS振荡器等一起使用,可为5G网络中的所有设备提供全套的精准时钟方案。可广泛用于RRU、AAU、BBU、Massive MIMO、5G Small cells 等相关产品中。

五、“Cascade”系列产品介绍

“Cascade”系列产品一功能简介:

集成MEMS谐振器消除了石英相关的性能和可靠性问题

灵活的输入输出频率转换和抖动衰减,4个输入,多达11个输出

宽输出频率支持

8 kHz至2.1 GHz的差分输出

从8 kHz到250 MHz的LVCMOS输出

1 PPS(每秒脉冲数)输出

宽输入频率支持

从8 kHz到750 MHz的差分输入

从8 kHz到250 MHz的LVCMOS输入

可单独配置的输出格式和VDD电源

LVPECL、CML、HCSL、LVDS或LVCMOS

1.8V、2.5V或3.3V

每个PLL的可编程抖动衰减带宽:1 mHz到4 kHz

同步、保持或自由运行运行模式

锁定到有间隙的时钟输入以支持OTN

切换准同步时钟的可编程频率斜坡

通过I2C或SPI的DCO模式,分辨率为0.005 ppb

可编程输出延迟控制

芯片状态监测指标:锁丢失、时钟丢失、频率漂移

工业标准64针9 x 9毫米封装

ymf

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)