LS码及其FPGA的实现

引 言

众所周知,在二元域、有限域以及复数域都不存在理想的地址码,如m序列、Gold序列以及Walsh码的相关性都不理想,这使得采用传统扩频码的CDMA系统是一个自干扰系统,需要采用联合检测技术、智能天线技术以及更复杂的功率控制技术来抵抗ISI(码间干扰)、MAI(多址干扰)以及ACI(邻小区干扰)。LS(Loose Synchronized)码是由李道本教授发明的新型地址码,它利用互补码特性突破了Welch界的限制,构造出了具有零相关特性的地址码。只要“零相关窗”覆盖了多径时延,那么ISI和MAI都是不存在的。这样就将一个传统的通信系统从干扰受限转换为噪声受限系统,也就是说,整个系统只受到噪声的干扰,而且具有很高的频谱效率和数据传输速率。无需联合检测技术和智能天线技术,只需简单的功率控制技术,因此可以说,LS码是一项突破性的技术。

今天,FPGA在消费、汽车和工业领域的应用经历了爆炸式的增长,FPGA可以用于软件无线电、雷达、影像、片上系统(SoC)和其他数字信号处理领域。LS码在FPGA中实现扩频和解扩不仅具有很高的灵活性而且还有较好的数据传输可靠性,本文首先简单介绍了LS码的概念和构造原理,然后详细介绍了LS码扩频和解扩在工程上的实现。

1 LS码的构造和性质

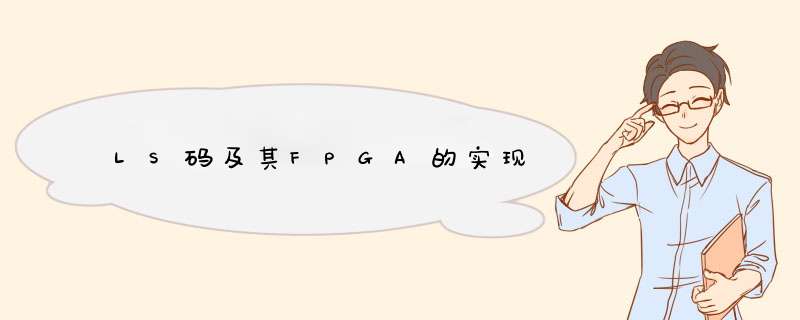

LS码由C码和S码构成,图1是LS码的树形构造法,除了树形结构生成方法外,还有多项式生成法、与联合检测相结合的组间零相关窗LS码构造法以及Kronecker内积法等,这些方法所生成的LS码都具有零相关窗的特性。

C码和S码各自的自相关值和互相关值在一定范围内大小相等、极性相反,因此它们的和在这个范围内为0,通常把相关值为零的范围称为“零相关窗”,在零相关窗内各地址码的自相关函数及互相关函数没有副峰。

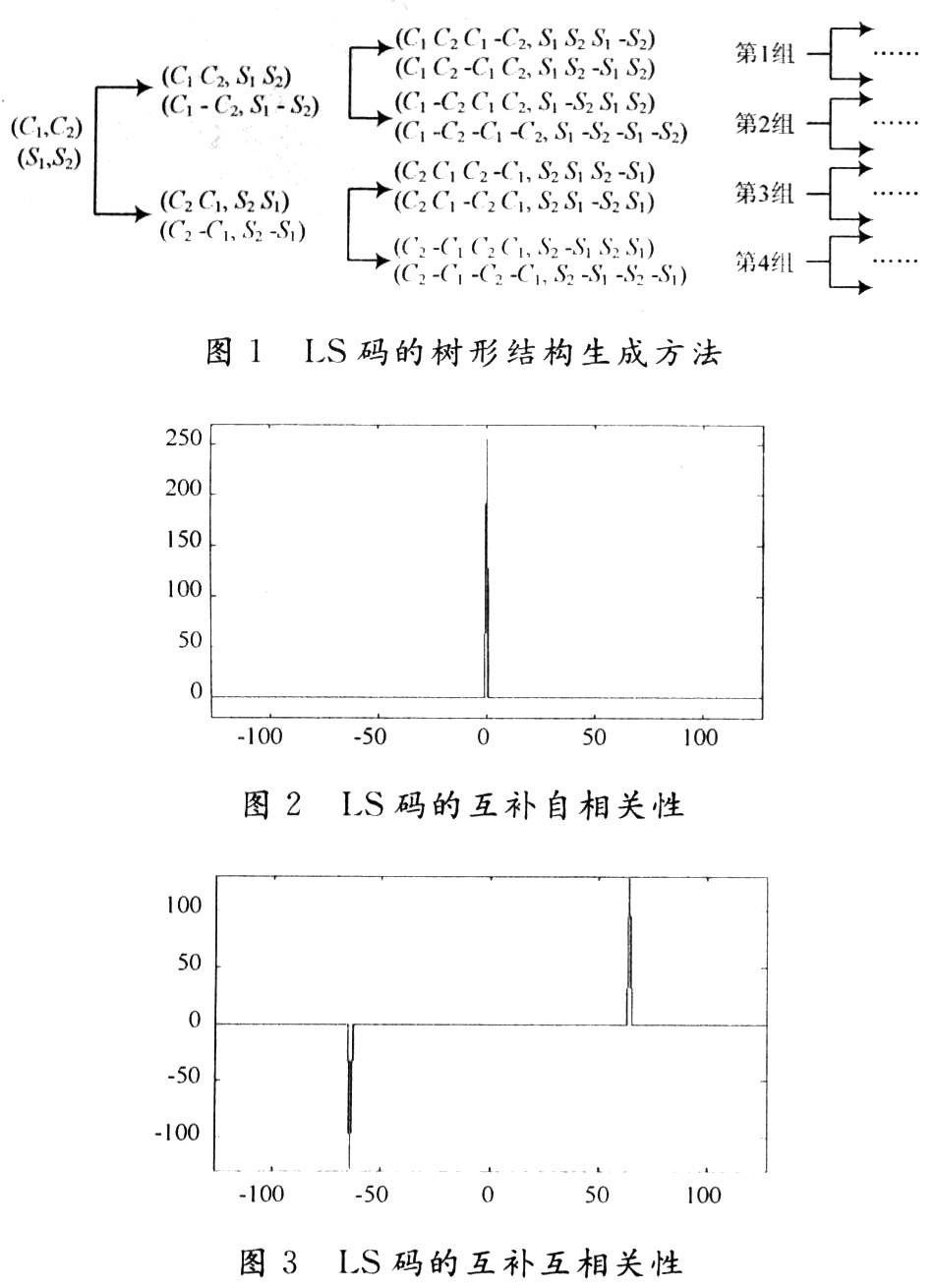

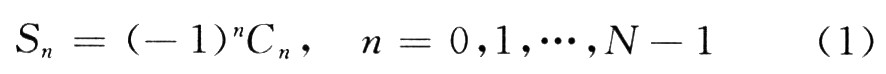

LS码的自相关特性如图2所示,从图中可以看出,LS码的自相关的副峰值除了原点外处处为0。由于LS码的特性,任意两个码字之间的“零相关窗”长度并不相同。图3是LS码的互相关特性,可以看出,LS码的互补互相关性在原点周围的一定范围内为0,这个范围也就是所谓的“零相关窗”,所选的两个LS码字的“零相关窗”长度为127。

2 LS码在FPGA中的实现

和一般的FPGA开发过程一样,LS码在FPGA中的实现需要经过可行性分析、算法验证、设计输入、仿真和下载测试几个过程。针对某个软件无线电平台的要求,可以合理地设计码速率和码长,扩频前的码速率为64 Kb/s,C码和S码的长度都为16,扩频后的码速率为1.024 Mb/s。

2.1 LS码的实现算法

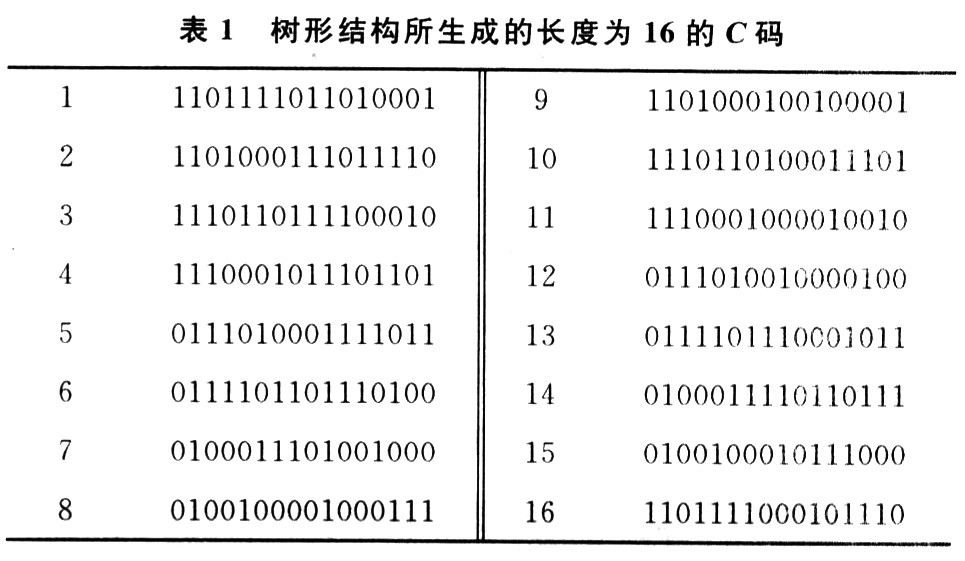

为了提高FPGA的处理效率,采用查找表的形式,首先生成了长度为16的C码和S码,生成码的算法是基于图1的树形结构,C码和S码关系为:

式中:n为C码和S码每一位的位置编号,N为码长。表1是所生成的长度为16,个数也为16的C码。S码可以根据式(1)求得,限于篇幅,这里不再单独列出,实验中只选取了表1中序号为1的一组C码和相应的S码作为查找表使用。

2.2 设计输入和仿真

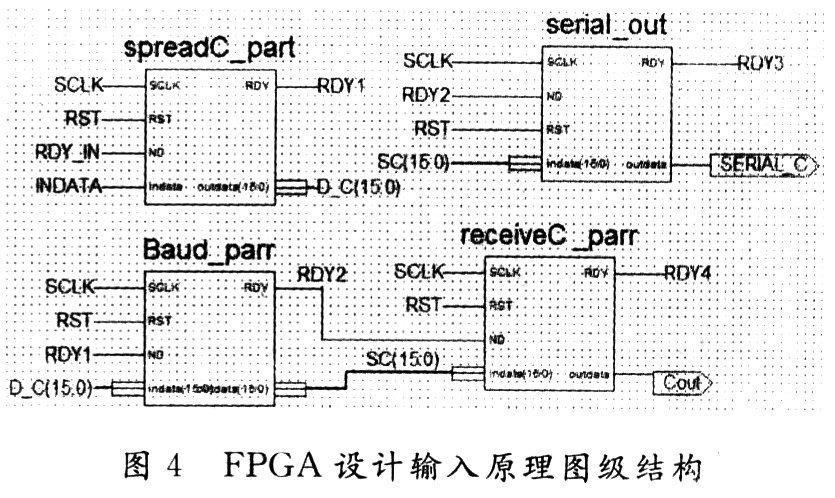

FPGA的设计输入有多种表达方式,最常用的是原理图方式和HDL文本方式,这里采用的是混合输入方式,首先采用Verilog HDL的文本输入方式将算法做成模块,然后再通过原理图的方式定义连接和接口,这样不仅使得逻辑描述性、可重用性和移植性强,而且使得接口描述和连接关系清晰、直观。图4是所设计的原理图结构,为了表示清楚,只截取了C码的扩频和解扩模块,其中spread C_part是C码的扩频模块,Baud_parr和serial_out模块的输出分别为并行输出和串行输出,这样做的目的是为了方便之后其他算法功能模块的输入,如果后面要加入例如调制、波形成型之类的模块,就可以方便地选择并行输入或者串行输入,提高了设计的灵活性。receiveC_parr为C码的并行解扩模块,这里只考虑了对Baud_parr所输出的并行数据进行解扩,这样能提高接收端的处理效率。输入端口SCLK为32.768 MHz的时钟,输出端口SERIAL C为seri al_out模块的串行输出,Cout为receiveCparr模块的解扩输出。

在设计中,spreadC_part模块的扩频输出速率并不是所需的码速率,而是经过Baud_parr和serial_out模块后再构成所需的码速率。

当完成设计输入后,就需要对所设计的算法进行时序仿真,验证算法的正确性。图5的时序图是采用ModelSim对C码的扩频模块spreadC_part、扩频的并行输出模块Baud_parr、串行输出模块serial_out以及并行解扩模块receiveC_parr所进行的仿真时序。如图5所示,Baud16x是一个1.024 MHz的时钟,INDATA是速率为64 Kb/s的输入码元、D C(15:0)为spreadC_part模块输出的扩频数据。注意到此时的D_c(15:0)为总线结构的16位数据,速率为Baud16x/8=128 Kb/s,在空闲时刻输出的都是0,这个数据输入到Baud_parr模块和seriaI_out模块。SC(15:0)和SERIAL_C分别对应这两个模块的并行输出和串行输出。可以看出SC(15:0)是16位总线数据,速率为1.024 Mb/s,SERIAL_C的串行数据速率也为1.024.Mb/s。Cout为将SC(15:0)的并行数据解扩后恢复出来的码元,可以看出,Cout正确地恢复出了IN-DATA的码元。

3 FPGA的下载测试

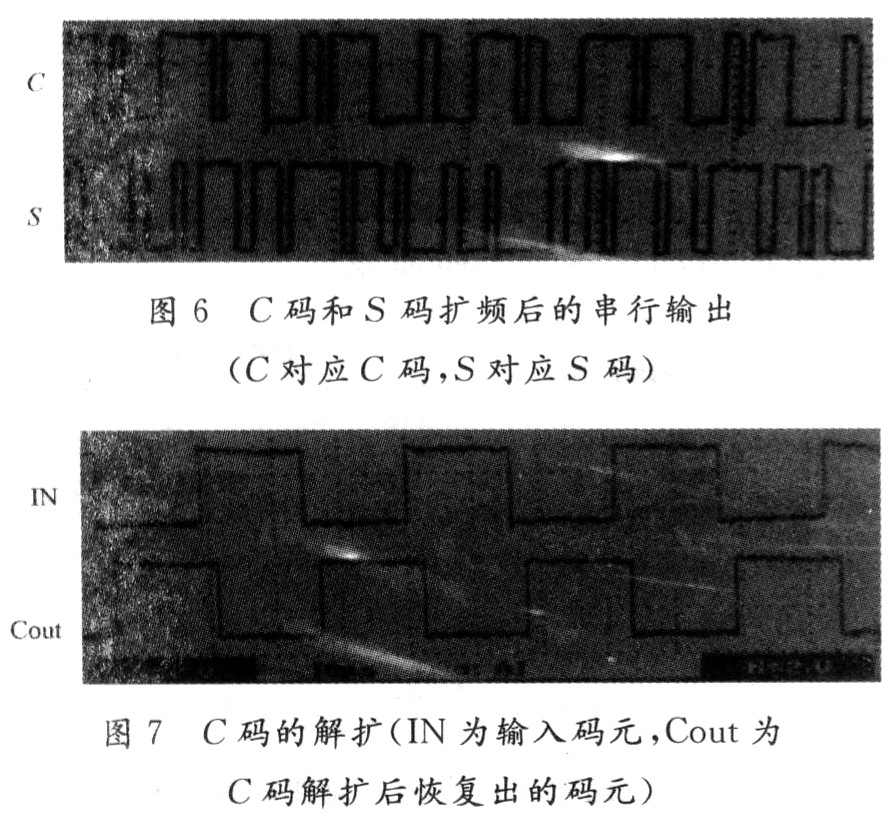

完成了设计输入和仿真后,就可以进行FPGA的下载测试,所针对的是基于Xilinx Spartan2S-300E的FPGA芯片的硬件环境。图6~图8是使用FLUKE199C型示波器观测到的波形。其中,图6是C码和S码分别扩频后的串行模块serial_out输出,图中的每一虚线单元格对应10 μs,可以粗略算出此时的串行速率大约为1 Mb/s,与所需1.024 Mb/s基本吻合。

图7和图8分别是C码和S码解扩后的输出与原始的数据码元IN的比较,可以大致估算出Cout和Sout的数据速率大约为64 Kb/s,测试结果表明所设计正确,硬件平台运行稳定。

4 结 语

本文通过对LS码在FPGA中的实现进行了研究,介绍了LS码的构造和相关性,主要介绍了LS码构造的算法验证,FPGA的设计输入、仿真以及下载测试,仿真和测试的结果表明所设计的输出正确,达到了预期的目的。今后的工作主要包括LS码在FPGA中的调制、解调、同步等算法的实现。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)