基于ARM+FPGA的重构控制器设计

可重构技术是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。常规SRAM工艺的FPGA都可以实现重构,利用硬件复用原理,本文设计的可重构控制器采用ARM核微控制器作为主控制器,以FPGA芯片作为协处理器配合主控制器工作。用户事先根据需求设计出不同的配置方案,并存储在重构控制器内部的存储器中,上电后,重构控制器就可以按需求将不同设计方案分时定位到目标可编程器件内,同时保持其他部分电路功能正常,实现在系统灵活配置,提高系统工作效率。

1 SVF格式配置文件

很多嵌入式系统中都用到了FPGA/CPLD等可编程器件,在这些系统中利用SVF格式配置文件就可以方便地通过微控制器对可编程器件进行重新配置。目前可编程芯片厂商的配套软件都可以生成可编程器件的SVF格式配置文件,串行矢量格式(SVF)是一种用于说明高层IEEE 1149.1(JTAG)总线 *** 作的语法规范。SVF由Texas Instruments开发,并已成为数据交换标准而被Teradyne,Tektronix等JTAG测试设备及软件制造商采用。Xilinx的 FPGA以及配置PROM可通过JTAG接口中TAP控制器接收SVF格式的编程指令。由于SVF文件由ASCII语句构成,它要求较大的存储空间,并且存储效率很低,无法胜任嵌入式应用。为了在嵌入式系统中充分利用其有限的存储空间,并不直接利用SVF文件对可编程器件进行在系统编程,而是将SVF文件转换成另一种存储效率比较高的二进制格式的文件,把它存储在数据存储器中。Xilinx公司提供用于创建器件编程文件的iMPACT工具,该工具随附于标准Xilinx ISETM软件内。iMPACT软件能自动读取标准的BIT/MCS器件编程文件,并将其转换为紧凑的二进制XSVF格式。

本设计是基于“ARM处理器+FPGA”结构的重构控制器,重构控制器中的FPGA能够根据ARM处理器传送来的命令,对目标可编程器件 JTAG接口进行控制,并负责解译XSVF格式的配置文件信息,生成xilinx器件所用的编程指令、数据和控制信号(TMS,TDI,TCK序列)向目标可编程器件的JTAG TAP控制器提供所需的激励,从而执行最初在XSVF文件内指定的编程和(可选的)测试 *** 作。使目标可编程器件内的TAP状态机进行状态转换,将指令和数据扫描到FPGA内部边界扫描电路指令寄存器和数据寄存器中。完成一次目标可编程器件配置,实现用户此时所要求功能,在下一时段,可根据用户新的要求,调用重构控制器内部存储器中不同方案在系统重新配置目标可编程器件,这样就实现了硬件复用,减少成本。

2边界扫描(JTAG)原理

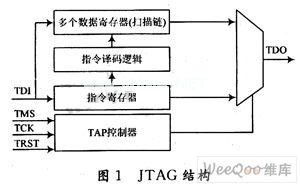

2.1 JTAG接口基本结构

JTAG(Joint Test,AcTIon Group,联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),其工作原理是在器件内部定义一个测试访问端口(TestAccess Port,TAP),通过专用的JTAG测试工具对内部节点进行测试和调试。TAP是一个通用的端口,外部控制器通过TAP可以访问芯片提供的所有数据寄存器和指令寄存器。现在JTAG接口还常用于芯片的在线配置(In-System Programmable,ISP),对PLD,FLASH等器件进行配置。JTAG允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,实现对各个器件分别测试和在系统配置。

JTAG主要由三部分构成:TAP控制器、指令寄存器和数据寄存器,如图1所示。标准的JTAG接口有四组输出线:TMS,TCK,TDI,TDO,以及1个可选信号TRST。

TCK:JTAG测试时钟输入,当TCK保持在零状态时,测试逻辑状态应保持不变;

TMS:测试模式选择,控制JTAG状态,如选择寄存器、数据加载、测试结果输出等,出现在TMS的信号在TCK的上升沿由测试逻辑采样进入TAP控制器;

TDI:测试数据输入,测试数据在TCK的上升沿采样进入移位寄存器(SR);

TDO:测试数据输出,测试结果在TCK的下降沿从移位寄存器(SR)移出,输出数据与输入到TDI的数据应不出现倒置;

TRST:可选复位信号,低电平有效。

Xilinx器件接受使用JTAG TAP的编程指令和测试指令。在IEEE 1149.1的标准中,用于CPLD,FPGA以及配置PROM的常见指令有:旁路(BYPASS)指令,通过用1 b长的BYPASS寄存器将TDI与TDO直接连接,绕过(即旁路)边界扫描链中的某个器件;EXTEST指令,将器件I/O引脚与内部器件电路分离,以实现器件间的连接测试,它通过器件引脚应用测试值并捕获结果;IDCODE指令,返回用于定义部件类型、制造商和版本编号的32位硬件级别的识别码; HIGHZ指令,使所有器件引脚悬置为高阻抗状态;CFG_IN/CFG_OUT指令,允许访问配置和读回所用的配置总线;JSTART,当启动时钟= JTAGCLK时为启动时序提供时钟。

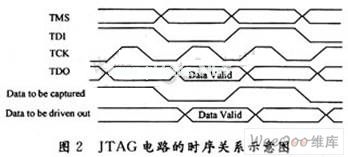

2.2 Tap状态机时序介绍

JTAG边界扫描测试由测试访问端口的TAP控制器管理。TMS,TRST和TCK引脚管理TAP控制器的 *** 作,TDI和TDO位数据寄存器提供串行通道。TDI也为指令寄存器提供数据,然后为数据寄存器产生控制逻辑。对于选择寄存器、装载数据、检测和将结果移出的控制信号,由测试时钟 (TCK)和测试模式(TMS)选择两个信号控制。测试复位信号(TRST,一般以低电平有效)一般作为可选的第五个端口信号。

如图2所示,所有基于JTAG的 *** 作都必须同步于JTAG时钟信号TCK。所有测试逻辑的变化(例如指令寄存器,数据寄存器等)必须出现在 TCK的上升沿或下降沿。关键时序关系是:TMS和TDI采样于TCK的上升边沿,一个新的TDO值将于TCK下降边沿后出现,因此一般情况下JTAG的时钟不会太高。

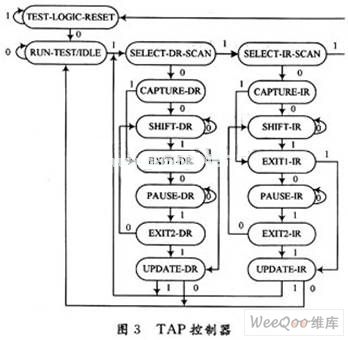

图3表示了IEEE 1149.1标准定义的TAP控制器的状态图,TAP控制器是16个状态的有限状态机,为JTAG接口提供控制逻辑。TAP状态转移如图3所示,箭头上的 1或0,表示TMS在TCK上升沿的值(高电平TMS=1,低电平TMS=0),同步时钟TCK上升沿时刻TMS的状态决定状态转移过程。对于TDI端输入到器件的配置数据有两个状态变化路径:一个用于移指令到指令寄存器中,另一个用于移数据到有效的数据寄存器,该寄存器的值由当前执行的JTAG指令决定。当TAP控制器处于指令寄存器移位(SHIFT-IR)状态时,对于每一个TCK的上升沿,连接在TDI和TDO之间的指令寄存器组中的移位寄存器向串行输出方向移一位。

当TMS保持为高电平时,在TCK的上升沿TAP控制器进入到“EXIT1-IR”状态;当TMS为低电平时,TAP控制器保持在“指令寄存器移位”状态。

3重构控制器设计

3.1硬件系统组成

其主要功能是控制按照用户不同需求控制调用不同的方案配置目标可编程器件。它主要包括ARM处理器、FPGA、FLASH存储器和对外总线接口,各功能部件主要功能如下:

(1)ARM处理器选用AT91FR40162S,其主要功能是控制模拟JTAG接口的FPGA读取FLASH存储器中的重构方案,实现在系统配置;

(2)FPGA协处理器选用Xilinx公司SPARTEN3AN系列的XC3S700AN-FGG484,是基于非易失性存储的FPGA,自身带有PROM,它作为外部总线和ARM控制器之间的双端口,主要功能是模拟JTAG接口实现TAP控制器时序,完成配置方案数据的并串转换并输出至外部总线;

(3)FLASH存储器容量为32M×16 b,用于处理器的上电引导、存放多种重构配置方案。由于要求的存储容量较大,采用SPANSION公司S29GL512P(32M×16 b)的存储空间,访问速度为110 ns,可以达到25 ns快速页存取和相应的90 ns随机存取时间,FBGA封装;

(4)外部总线接口,可采用1路RS 232驱动接收器,实现和外部通信的接口;

(5)测试线TCK,TMS,TDI和TDO,是重构控制器向目标可编程器件提供所需的JTAG TAP激励,分别控制目标多个FPGA的重构配置和反馈重构信息。

3.2重构控制器工作原理

ARM执行的初始化工作包括程序更新加载运行,FPGA参数设定等;FPGA设定内部寄存器和逻辑状态的初始值、内部缓冲区数据清零等。

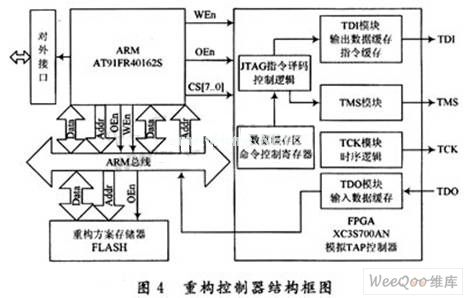

重构控制器示意图如图4所示。图中ARM处理器一方面通过ARM总线读取外部FLASH中的配置方案,对其进行并串转化 *** 作,将其存储到 FLASH存储器中;另一方面重构控制器中模拟TAP控制器的FPGA,从ARM内置的FLASH存储器中读取配置文件,并执行ARM处理器发出的指令解译该文件,重构控制器解释二进制文件方法如下:在ARM处理器的控制下,从装载配置文件的FLASH中读出一个字节,判断是哪条JTAG指令,然后根据指令的格式作具体的处理,产生TCK,TMS,TDI和TDO信号,作为目标可编程器件的JTAG接口激励,与目标可编程器件的JTAG口串联成菊花链,在 ARM处理器的控制下,对目标可编程器件进行在系统编程。被重构的FPGA由支持局部动态重构的Xilinx公司的Virtex-4系列FPGA来实现。

4 结 语

本文介绍的重构控制器既具有ARM微控制器所拥有的高速处理器核、体积小、集成度高、运算速度快、存储器容量大、功耗低等特点,又具有FPGA 强大的并行计算能力和方便灵活的动态可重构性,使硬件信息(可编程器件的配置信息)像软件程序一样被动态调用或修改。对于特定的目标FPGA芯片,在一定控制逻辑的驱动下,对芯片的全部或部分逻辑资源重新进行动态配置,从而实现硬件的时分复用,灵活快速地改变系统功能,节省逻辑资源,满足大规模应用需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)