作者:姚旺君,林浩,王永利,邢计元,张鹏

引言

EtherCAT是由BECKHOFF提出和设计的一种工业以太网现场总线技术,广泛应用于运动控制领域。

EtherCAT主要优势在于高速、高实时性以及精确时钟同步。这些优势的实现基于EtherCAT设计的几个关键技术:飞读飞写(processing on the fly)、FMMU(Fieldbus Memory Management Unit)、DC(Distribute Clock)。以上几个关键技术都是在EtherCAT从站控制器ESC(EtherCAT Slave Controller)中实现,ESC是实现EtherCAT通信协议的关键。

目前,EtherCAT从站控制技术由国外掌握,IP核和芯片全部是由国外公司提供。我国正在执行智能制造2025国家战略,没有自主化的先进的工业现场总线,工业系统升级就只能是亦步亦趋,跟随国外公司的步伐,无法开发出具有自主创新技术的专用产品。在工业控制系统领域,国外工业控制系统企业占据竞争优势,然而,工业现场总线是工业控制系统运行的枢纽,无论什么数据都要经过这个枢纽进行传输,出于系统安全的考虑,有必要对工业现场总线进行研究,以实现自主化设计。目前国内已经有针对EtherCAT总线技术的研究的:文献[5]设计并验证了ESC实现的通信链路可行性,文献[6]提出了一种使用FPGA实现FMMU的算法,但是上述研究都是进行理论推导与算法设计,没有工程实践应用。针对该问题,本文基于FPGA依据EtherCAT工作原理,设计一种能满足工程实践的EtherCAT功能单元FMMU,实现了FMMU的地址映射以及数据字节和位提取的功能。

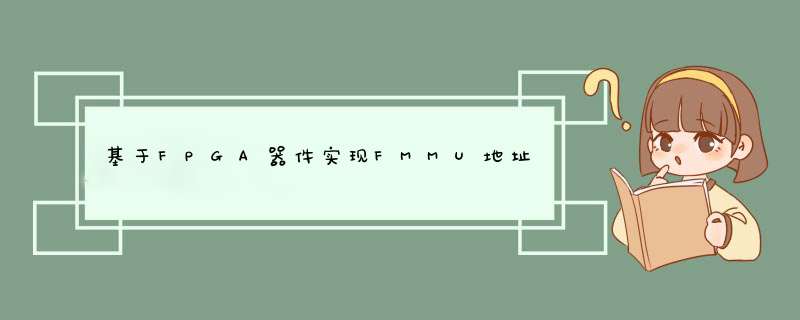

1 EtherCAT系统及功能组成

EtherCAT主站与从站组成结构如图1所示。主从站的单次通信过程是:主站遍历所有从站设备,数据帧通过某一从站时,从站设备根据报文命令分析寻址到本机报文并定位到指定位置进行数据读/写,数据帧到达最后一个从站后,该从站把处理后的数据帧发送给主站。主站收到此上行电报后处理并返回数据,一次完整的通信过程结束。EtherCAT系统整个通信过程由主从站内部状态机控制,主站采用广播寻址、自增量寻址、配置地址寻址、逻辑寻址等寻址方式和命令,这个阶段,主站获取了所连从站的基本信息,从站也根据主站数据帧要求对自身进行配置,有过程数据要求的对相关从站的FMMU进行配置,这些工作完成后,主从站转入OP(OperaTIon)态。

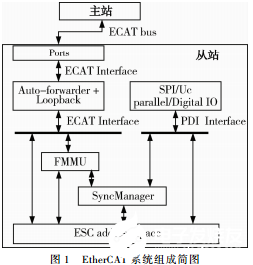

EtherCAT从站控制器IP主要包括端口控制(Ports)处理单元、Auto-forwarder模块、Loopback模块、FMMU、SyncManager、PDI(Process Data Interface)单元、复位处理单元、分布时钟、EEPROM接口单元、REGS及RAM区,每个功能模块之间的关联如图2所示。根据不同的通信阶段及从站配置类型,EtherCAT可通过FMMU直接访问从站控制器的地址控制,读写RAM或寄存器区;有的从站过程数据交互时必须先通过SyncManager,才能对RAM或寄存器区进行读写访问,其中SyncManager是为了数据一致性以及数据安全性而设计的,既用作访问RAM或寄存器区的管理单元,又可以作为PDI和ECAT数据同步的调度接口。

2 FMMU原理及实现

2.1 FMMU运行原理

FMMU作为EtherCAT从站控制器的核心功能之一,采用地址映射技术将主站的逻辑地址转换为从站的物理地址,映射地址空间达4 GB。FMMU用于主站对于从站的逻辑寻址命令帧中,而且能在一个数据子帧中对多个分布式从站进行寻址,既能节约数据帧资源,提高数据帧利用率,又能方便主站本地的地址空间管理和分配。

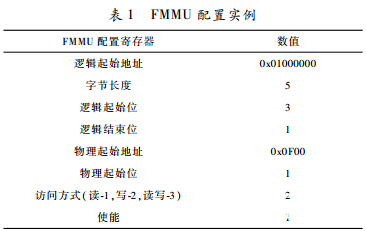

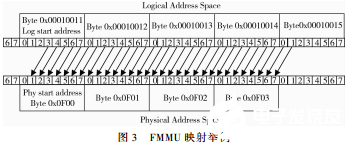

EtherCAT系统运行时,每个EtherCAT从站都有一个配置文件,即ESI(EtherCAT Slave InformaTIon)文件,规定了每个从站的软件版本、类型、资源配置包括FMMU个数等情况。主站利用配置工具,将每个从站的ESI文件作为输入生成ENI(EtherCAT Network InformaTIon)文件,主站软件根据各个ENI文件了解自身所在EtherCAT网络的从站信息。主站运行起来后会根据ENI文件要求对各个从站进行配置,FMMU就是由主站在PREOP到SAFEOP状态转换过程中进行配置的,主站根据每个从站的ENI信息对相关从站的FMMU配置以下信息:主站逻辑起始地址、字节长度、逻辑起始位、逻辑结束位、从站物理起始地址、从站物理起始位、访问方式(读、写、读写)、使能。映射实例如表1和图3所示。

本实例是将32位的主站逻辑地址0x00014708映射到本地从站物理地址0x0F05,从实例配置表中可以看出,逻辑映射起始位为bit 5,结束位为bit 3,映射长度为7 bit, *** 作类型是写。

从站FMMU是由主站在PREOP状态利用FPWR(Configured Address Physical Write)命令进行配置的。从站配置成功,并且系统转入OP状态之后,在进行过程数据的交互时,从站会收到主站发出的逻辑寻址的EtherCAT子报文,根据各个从站的FMMU逻辑配置情况,查询是否有与子报文中逻辑地址区相匹配的区域,如果有,且为输入类型数据(主站读访问 *** 作),则从站FMMU会将映射的物理地址区数据插入到EtherCAT子报文数据区的对应位置;如果配置逻辑地址在子报文逻辑地址区域内且为输出类型数据(主站写访问 *** 作),则从站FMMU根据配置要求将逻辑地址区数据抽取到被映射的相应物理地址区。

2.2 FMMU实现原理

根据以上FMMU运行原理及配置实例分析,可将FMMU的实现原理分为两部分:FMMU配置设计与实现、FMMU数据处理设计与实现。

2.2.1 FMMU配置设计与实现

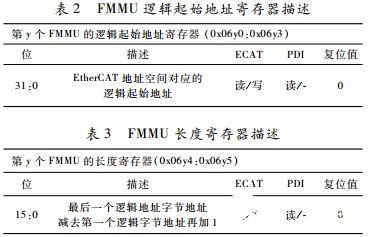

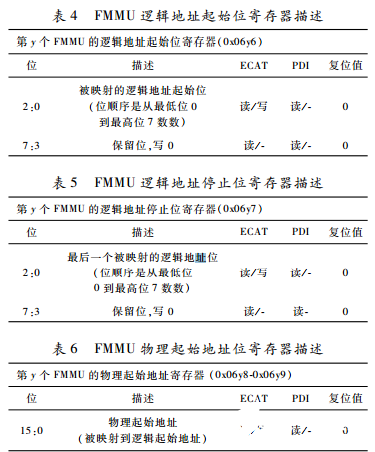

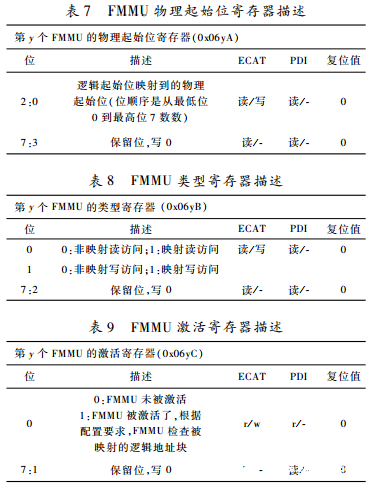

根据EtherCAT协议和规范,从站的FMMU只能由主站进行配置,配置寄存器的基地址为0x0600开始的256B(FMMU个数为8,每个FMMU配置寄存器个数为16)的区域,表2~9所示为FMMU的所有配置寄存器描述说明(其中y表示FMMU索引,值为0~15)。

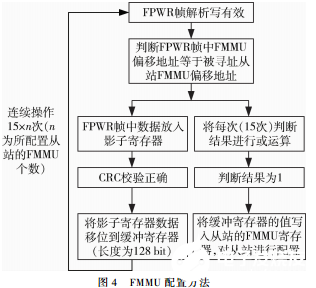

FMMU的配置实现过程(即在PREOP状态,主站发FPWR命令帧进行配置)如图4所示。从站FPGA根据EEPROM配置的FMMU个数(0x0004寄存器的值,即图中变量n)依照图4所示逻辑对从站的FMMU进行配置,配置的逻辑地址起始位要大于等于配置的物理地址起始位。

2.2.2 FMMU数据处理-主站读

主站发LRD(逻辑读)或者LRW(逻辑读写)命令帧,通过FMMU对从站进行读 *** 作,读 *** 作分为按位读(bit-wise reading)和按字节读 (byte-wise reading)两种方式,按位读支持对从站任何允许的地址区域 *** 作。逻辑读 *** 作处理逻辑为: FPGA代码判断访问类型是否为读配置、帧命令是否为LRD和LRW、地址是否在逻辑映射地址区间内,满足这三个条件后,置一个标志位,在此标志位为1的情况下,将被映射的物理地址中的数据插入到数据帧的逻辑地址空间。

2.2.3FMMU数据处理-主站写

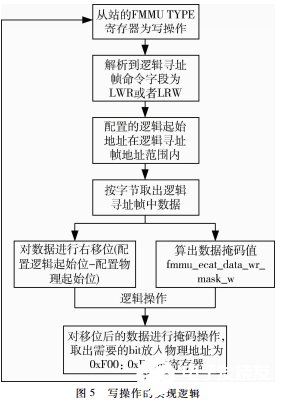

主站发LWR或者LRW命令帧,通过FMMU对从站进行写 *** 作,写 *** 作分为按位写和按字节写两种方式。对于按位 *** 作来说,对同一个从站内的两个FMMU都进行按位写 *** 作的情况下,两个FMMU的逻辑起始地址之差值设置为大于等于3。对于按字节 *** 作来说,没有这个限制。按位写只支持对从站地址区域为0x0F00:0x0F03的数字量输出寄存器的按位写 *** 作,对于除此区域之外的其他地址区域的按位写 *** 作,未映射的区域将会被写入非定义的值,按字节写没有这种区域限制。图5所示为写 *** 作的实现逻辑。

在写 *** 作的实现逻辑中,通过设置掩码,将需要写入的bit置1,不需要写入的bit置0,然后将掩码与原先物理地址区域或寄存器中的原值进行逻辑运算,既将要写入的bit写入了物理寄存器中,又保留了不需要更新的物理寄存器中的原值保留。

3 功能测试

功能测试选取LWR命令进行验证,对两个从站采用按位写的映射方式。通过在testbench(测试台)中编写EtherCAT逻辑写测试包激励,使用Modelsim对设计的FMMU模块设计进行仿真测试,验证从站0xF00:0xF03中最终被写入数据的正确性。

3.1 测试例说明

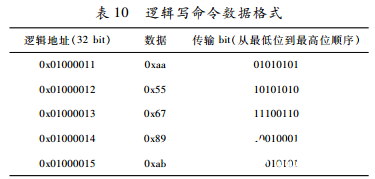

测试例采用两个从站,从站的0xF00:0xF03寄存器值默认复位都为0;主站采用LWR命令,逻辑起始地址0x01000011,写入5B数据0xaa556789ab,网络协议采用高字节顺序,即高字节数据存放在低字节地址,而且在传输中最先传输最低位,数据格式见表10所示。

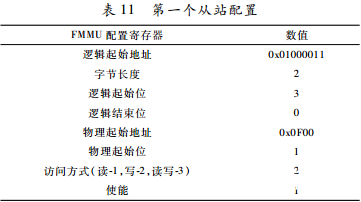

第一个从站的配置如表11所示,假设此从站物理寄存0x0F00:0F03初始值为0xabcdef78,按FMMU实现原理分析,FMMU模块截取逻辑写帧的值应该为6 bit: 010100,写入到物理寄存器0x0F00:0x0F03(leastbit:10101001即为0x95)的值为0x95cdef78。

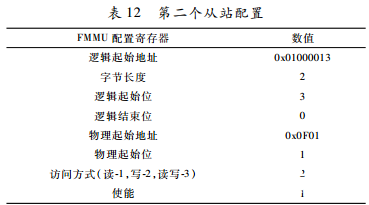

第二个从站的配置如表12所示,假设此从站物理寄存0x0F00:0F03初始值为0x12345678;按FMMU 实现原理分析,FMMU模块截取逻辑写帧的值应该为6 bit: 001101,写入到物理寄存器0x0F00:0x0F03(leastbit:00011010即为0x58)的值为0x12585678。

3.2 仿真测试验证

仿真采用Modelsim软件进行,根据表11和表12的配置要求,对从站1和从站2分别进行逻辑按位写仿真验证。

根据表11中第一个从站的测试例,取主站逻辑地址0x01000011中的数据0x55,得到的mask为0x3E00,处理后的数据为0x1540;取主站逻辑地址0x01000012中的数据0xaa,得到的mask为0x0040,处理后的数据为0x2a95,如图6所示。

对数据进行掩码 *** 作处理,将物理地址0x0F00 中bit1~bit6对应的6 bit数据用逻辑地址0x01000011对应的bit3开始的6 bit数据替换,得到从站1的物理地址0x0F00的数据为0x95,数据处理仿真结果如图7所示。

根据表12中第二个从站的测试例,取主站逻辑地址0x01000013中的数据0x89,得到的mask为0x3E00,处理后的数据为0x19C0;取主站逻辑地址0x01000014中的数据0x67,得到的mask为0x0040,处理后的数据为0x2295,如图8所示。

对数据进行掩码 *** 作处理,将物理地址0x0F01 中bit1~bit6对应的6 bit数据用逻辑地址0x01000013对应的bit3开始的6 bit数据替换,得到从站2的物理地址0x0F01的数据为0x58,数据处理仿真结果如图9所示。

4 结论

通过对FMMU实现逻辑代码的Modelsim仿真数据结果,验证了FMMU原理及其逻辑实现的正确性,说明用FPGA实现EtherCAT从站控制器FMMU模块是完全可行的,为开发完善的ESC从站控制器创造了条件。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)