利用集成式接收器简化数字预失真电路模拟部分

数字处理电源领域的巨大进步引发了对高性能模拟产品的更大需求。除传统语音外,如今的蜂窝网络还能够以前所未有的高速率传输重要的数据和视频信息,这催生了新的调制方法和依赖于复杂数字技术的新型空中接口标准。尽管数字技术使系统能够在采用更小封装尺寸且具有更高可靠性的情况下运行更快速、消耗功率更少,但是它们也对整个系统的RF和模拟信号采集部分提出了新的要求。

调制的复杂度以及基站发送器的宽带宽,导致功率放大器(PA)有更高的峰均比。为了满足较高峰均比存在下更严格的要求,PA一般尺寸很大,能够在线性区工作。如果没有数字校正,PA的效率可能在 10% 左右,这意味着要运行一个20W的PA需要200W功率。在基站中,PA消耗的电功率最大,因此就蜂窝服务供应商而言,PA对运营成本的影响也很大。为了提高PA效率,需要采用数字技术实现振幅因数降低(CFR)和数字预失真(DPD) 。

尽管驱动放大器进入饱和状态时放大器的效率最高,但是在饱和状态,放大器是高度非线性的。复杂的数字调制需要PA提供极高的线性度,这意味着必须驱动PA远离饱和状态。如果有办法补偿放大器固有的非线性,那么让PA恰好在即将进入饱和状态时工作,可以提供高效率。目前,DPD已经成为PA线性化的首选方法。

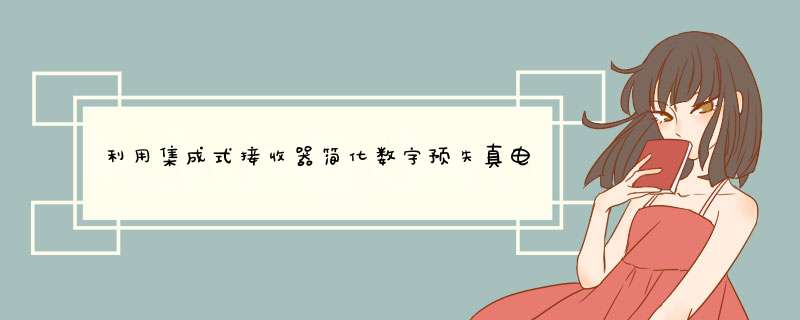

DPD是一种反馈方法,可以对PA的输出进行采样并将其转换为数字数据。将一个存储在FIFO中的无失真发送信号与反馈信号进行比较,并产生一个反传递函数。在CFR之后,将其与发送数据相加,以降低PA输出中的非线性。可以使用自适应算法或查找表来产生补偿数字信号,或结合使用这两种方法,但是这超出了本文讨论的范围。下面,我们将集中讨论对PA输出采样的接收器的模拟要求。

对数字预失真接收器的要求

该接收器是从 RF向数字化(参见图1)转换的信号链路。关键的设计要求是输入频率范围和功率级、中频以及将被数字化的带宽。这些要求中,有些直接来自PA规格,有些则是在设计时优化得到的。

图 1:数字预失真信号链路

基带发送信号上变频至载波频率,该信号频率由WCDMA、TD-SCDMA、CDMA2000、LTE等新空中接口标准定义。因此,被采样的输出频谱存在于定义好的频率范围(及期望信道)内。既然DPD环路的目的是测量PA的传递函数,那么就不必在多载波系统中分离载波,或调制数字数据。唯一必要的,是捕获有关整个期望信道的信息。

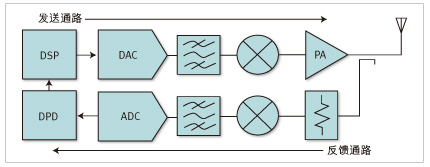

PA非线性会产生奇数阶互调分量,在相邻和相间信道中形成频谱再生。按照定义,三阶分量出现在2fa + fb、2fb + fa、2fa – fb和2fb – fa,其中的fa和fb是位于期望信道之内的两个信号频率(在信道外会引起互调失真)。对于一个已调制信道,三阶分量出现在期望信道三倍带宽的范围(见图2)。同样,五阶分量出现在五倍带宽的范围内,而七阶分量则出现在七倍带宽的范围内。因此,DPD接收器必须获得发送带宽的倍数,该倍数与正在进行线性化处理的互调分量的阶次相等。

图 2:互调分量

目前的发展趋势是,将期望信道与中频 (IF) 混合,并获得所有互调分量的完整带宽。选择恰当的IF以减少滤波负担,避开已经根据规格要求固定了的其它频率。类似地,选择整倍于数字调制芯片速率的值为采样速率,例如,在 WCDMA 中为 3.84MHz。最后,奈奎斯特定理决定,采样速率必须至少是被采样带宽的两倍。很多配置可以被接受的,其中满足上述限制的一种配置是:184.32MHz 中频、245.76MHz ADC 采样率和122.88MHz 带宽。

在 20W PA情况下,平均输出功率是43dBm。峰值/均值(PAR)约为15dBm。为了将进入接收链路混频器的平均输入功率设置为 -15dBm,耦合器和衰减器合起来的插入损耗必须是 58dB(参考图 1) 。WCDMA 标准中规定的PA带内噪声最大,为 -13dBm/MHz(-73dBm/Hz) 。因此,耦合器、衰减(-58dB)以及PA噪声限制(-13dBm/MHz)的结合,产生必须低于 -71dBm/MHz (-131dBm/Hz) 的接收器灵敏度等级。为了提供充足的裕度,应该在所期望的数字上再加上 6dB至10dB的裕值。这为DPD接收器设定了频率计划、功率级和灵敏度要求。

集成式数字预失真接收器

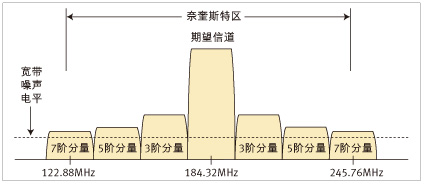

一旦定义了系统要求,接下来的任务就变成了用一个混频器、IF放大器、ADC、无源滤波、匹配网络和电源旁路来实现电路。尽管计算和仿真有所帮助,但是其无法取代对真实硬件的评估,硬件评估通常会一次一次反复产生多个PCB。然而,一类新型基于系统级封装(SiP)的集成式接收器极大简化了这一任务。例如凌力尔特的LTM9003数字预失真uModule接收器,该产品是一款全集成化DPD接收器,实质上是“射频到比特流”架构。

由凌力尔特公司倡导的uModule技术利用了一种由双马来酰亚胺三嗪(BT)材料制成的薄型多层压合基底。该多层基底允许采用RF组件、标准引线键合IC裸片和传统的无源元件进行复杂电路设计。电路采用标准IC封装模塑料进行封装,而且,LGA焊盘布局也与当前的表面贴装方法相符。这样就造就了一个外形与直观感觉酷似传统IC的子系统,其经过全面测试,确保了IC的高可靠性,并把采用不同半导体工艺的元件与无源元件结合,与传统实现方案相比,占位面积更小。

LTM9003由一个高线性度 RF 下变频混频器、一个IF 放大器、一个L-C 带通滤波器和一个高速ADC组成 (参见图 3) 。导线连接的裸片组装确保总的外形尺寸高度紧凑,而且还允许基准和电源旁路电容与传统封装方法相比更加靠近裸片。这样做降低了噪声使ADC精度下降的可能性。该理念扩展到了高频布局方法中,并在LTM9003接收器链路中得到了贯穿使用。

图 3:LTM9003 集成式数字预失真接收器

集成消除了驱动高速ADC面临的很多挑战。线性电路分析无法解决ADC采样和保持切换动作导致的电流脉冲。传统电路布局需要多次重复,来定义一个输入网络吸收这些脉冲,该网络在带外也有吸收性,但是要与前述放大器一起无缝工作。IF放大器还必须在不增加失真的情况下驱动这个网络。克服这些挑战也许是LTM9003 μModule接收器潜在的最突出的属性。

无源带通滤波器是一个通带非常平坦的3阶滤波器。在中心频率为25MHz的频带内,它呈现了不到 0.1dB的纹波,而且在整个122MHz内,通带纹波仅为0.5dB。三阶配置可确保频率响应曲线的肩峰部具有单调特性,这一点对于许多DPD算法来说非常重要。

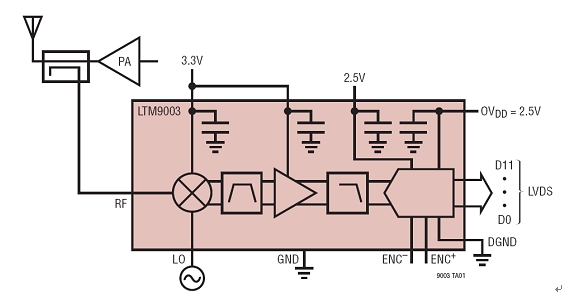

LTM9003的总体性能远远超过了上述系统要求。当使用一个-2.5dBm单音信号(相当于在ADC上的-1dBFS),信噪比的典型值为-145dBm/Hz。这个数字低于WCDMA标准定义的-131dBm/Hz目标值。最坏情况下谐波是60dBc。25.7dBm的IIP3数字意味着,如果PA具有足够的线性,那么LTM9003能够支持一个 87dBc 的 ACPR。相对于系统要求和可用最佳PA的功能而言,LTM9003远远超过了要求。整个链路供电电压为3.3V或2.5V,功耗1.5W,而且电路板面积仅为11.25mmx15mm。

图4:LTM9003 采用节省空间的 11.25mm x 15mm LGA 封装,运用多层基片屏蔽敏感模拟线路免受数字走线影响。

无需折中的灵活性

μModule技术还提供了意想不到的灵活性。传统的高集成电路,可能会在可编程模式或可选功能方面提供灵活度,但会增加复杂性,并常常导致某些性能缺失。通过改变无源元件的参数值或替代IC(作为一个组进行优化),LTM9003提供特殊版本,而且不会带来性能缺失或复杂性的增加。

例如:LTM9003-AA使用了一个3.3V电压供电的低功率、SiGe有源混频器。2xRF-2xLO分量产生了一个60dBc的二次谐波,这是频谱中的最差寄生干扰。这种情况可以通过使用相似的5V器件替换该混频器得到改善,但代价是功耗有所增加。于是,在LTM9003-AB中,二次谐波改善为6dB。同样,在LTM9003的另一版本中,可通过换用一个210Msps ADC(其功耗较小)来降低采样速率,并改变L-C滤波器的元件参数值实现100MHz带宽滤波器。该滤波器将针对通带平坦度和最佳信号链路性能进行优化,而且无需使用有损开关。更喜欢不同的IF吗? 只需变更少量无源元件参数值就可以如愿以偿。

绿色、小型化且易于使用

用LTM9003实现PA线性化的好处体现在几个不同的层面。在较高层面上,DPD使您能够以较少的补偿(back-off)运行PA。PA效率越高,就同样输出功率级别而言,消耗的功率就越少。正如之前讨论的那样,PA是基站中最重要的电消耗因素。如果你的公司有“绿色计划”,那么DPD能够为做些贡献。不管怎样,用更少的电可以降低服务供应商的运营费用,从而使其产品更具竞争力。

在电路板层,μModule封装将所有关键组件集成到非常小的面积上,其中包括用于滤波和去耦的无源组件。这节省了电路板空间、简化了布局并为能够进一步提高产品价值的其他功能留出了空间。

在工程层面上,LTM9003能够节省时间。滤波器设计和元件匹配处理可以在仿真过程中完成,但是在大多数场合中,需要进行重复以保证正确。设计一个不受 ADC采样和保持电路开关动作干扰的滤波器尤其具有挑战性。甚至如放置电容器来实现电源去耦这样常规的事情也可能影响整体性能,并可能导致电路板布局的修改。这些任务可能很容易耗掉几个月的工程设计时间,以对每一次修改进行调试,并评估这些改变。用LTM9003可以直接节省时间和资源。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)