本系统的主要功能是通过对语音信号进行压缩,以实现高效率数字录音,可用于电话留言,语声应答等场合。采用磁带录音实现电话留言,虽然录音的时间较长,但不便于查找和保存。数字录音可以克服磁带录音的缺点,不仅查找速度快,而且对录音信息进行编辑整理也非常方便,更为方便的是数字录音信息可以转存在计算机硬盘或光盘上以便长期保存。但是数字录音的缺点是要实现长时间录音需要很大的存储空间,因此本系统一方面采用存储量为16MB的单片闪速存储器KM29N160,另一方面采用2.0Kb/s的速率对语音进行压缩,采用这两种方法后,可以实现2小时以上的数字录音。

系统硬件设计

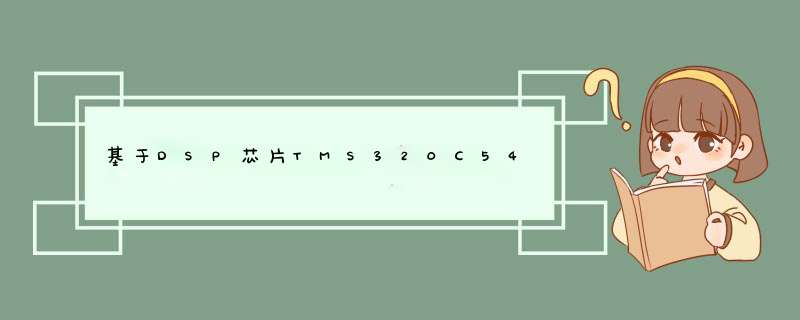

整个硬件设计包括三个部分,一是TMS320C5402 DSP处理系统,包括TMS320C5402、程序存储器、数据存储器、模数转换电路等;二是闪速存储器及其与TMS320 C5402的接口部分;三是AT89C51主处理器部分,包括AT89C51处理器、键盘显示电路及AT89C51与TMS320C5402接口。图1是整个硬件系统的示意框图。

图1 数字压缩语音录放系统硬件示意图

DSP处理系统

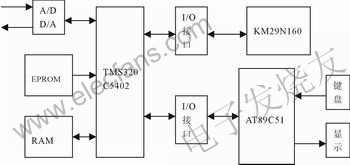

TMS320C5402 DSP处理系统主要完成语音的压缩和解压缩功能。系统主要由TMS320C5402、EPROM 27C256-15(1片)、高速RAM CY7C199-10(2片)、译码电路、晶体振荡器、模数转换电路等构成。其中,EPROM存储引导信息和程序代码,其地址为数据空间的8000H"FFFFH,DSP芯片加电运行时将EPROM中的程序代码搬移到高速RAM中。高速RAM的存取时间为10ns,可以全速执行,地址为0000H"7FFFH,共32K字,程序和数据均可访问。ADC采用Motorola公司的PCM编解码器MC14LC5480,这个芯片集语音A/D、D/A及抗混叠滤波于一体,采用单5V供电方式,TMS320C5402提供了可与PCM编码器等串行器件接口的串行口,因而只需将相应的引脚一一连接即可。其接口电路如图2所示。

图2 dsp与ADC的接口电路

主从系统设计

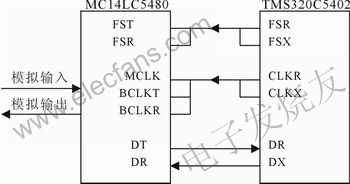

整个系统由AT89C51和TMS320C5402两个处理器以主从方式连接,其中AT89C51作为系统主机,完成系统的人机接口和对TMS320C5402的控制。单片机与DSP之间通过HPI-8连接,标准的HPI-8口是一个8位的并行端口,可以用来实现DSP和主设备或主处理器接口,双方通过共享TMS320C5402的片上存储器完成通信。单片机为主控部分,采用端口方式直接访问HPI口。HPI口主要由地址寄存器(HPIA)、控制寄存器(HPIC)、数据寄存器(HPID)、HPI存储器和HPI控制逻辑组成。对HPI口进行数据读写需要三个步骤:设置控制寄存器、写地址寄存器和读写数据寄存器。单片机和DSP的HPI口硬件接口如图3所示。

图3 单片机与DSP的HPI口硬件接口连接方法

系统软件设计

TMS320C5402的软件设计

TMS320C5402的软件包括EPROM引导程序和系统软件两部分。其中,EPROM引导程序比较简单,其作用是将系统软件从低速EPROM搬移到高速RAM中。系统软件由三部分组成:即主程序、串行中断服务程序和INT0中断服务程序。

主程序完成系统的初始化,包括从闪速存储器中读取已经存入的语音段数及数字音量等信息。完成初始化过程后,TMS320C5402就等待从AT89C51主处理器发来的各种命令,根据不同命令调用相应的处理程序。

串行中断服务程序完成语音的输入/输出和数据格式的转化功能,由于PCM编解码器输出的数据是8位m律数据,因此需将m律数据转化为线性格式的数据以便TMS320C5402进行处理。同样,TMS320C5402输出的线性数据也需转化为8位m律才能送至PCM编解码器进行D/A变换。

INT0中断服务程序主要用来接收从AT89C51送来的各种命令,并且设置相应的命令标志以便TMS320C5402在主程序中识别并调用相应的子程序。

AT89C51的软件设计

AT89C51软件主要包括初始化程序、主程序、定时中断服务程序和INT0中断服务程序。在初始化程序中,完成AT89C51的初始化、TMS320C5402的复位、从TMS320C5402获得已存入闪速存储器的语音段数和数字音量等。主程序主要是按键处理程序。定时器中断服务程序每隔10ms中断一次,增加程序所需的各种计数器的值,并置各种定时到达标志以便主程序判断使用。

结语

本文已经给出了硬件平台和软件设计思路,只要制作出硬件平台,并将仿真好的程序移植到dsp平台上就可以实现数字压缩语音录放,经试用具有很好的语音录放效果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)