自适应均衡器在LVDS息线长距离传输原理及应用

概述:自适应均衡嚣可自为信号损耗提供补偿,使电缆传来的串行数字信号可以重新恢复其原有强度。利用这一特点,采用高速串行数字接口(SDI)自适应电缆均衡器厦电缆驱动器芯片构建系统,可以扩大I,VDS技术的数据传送范围,以满足高速率条件下长距离传送的要求。详细介绍自适应电缆均衡器CLCO12的结构和工作原理;给出以Belden型同轴电缆和五类未屏蔽双绞线为载体进行实验的结果。

引 言

随着各式各样接入通信设备的应用,数据传输的需求急剧增加。系统设计工程师所设计的电路系统,必须支持数据的高速率传输。低电压差分信号LVDS(LOw-Vo1t—age DifferenTIal signal)便是这样一种技术。LVDS又称ANSI/TIA/EIA一644总线,是20世纪90年代才出现的一种性能优良的数据传输和物理层接口技术,为系统提供了高速数据传输、抑制共模噪声及降低功耗的能力。利用这种技术,可以设计数据传输系统,以确保能够支持千兆位以上的数据传输。理论上,LVDS的最高传输速率可达1.923Gbps。

LVDS技术的核心是采用极低的电压摆幅高速差分传输数据,可以实现点对点或一点对多点的连接;具有低功耗、低误码率、低串扰和低辐射等特点。其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。LVDS的发展不断衍生出各种新技术,如总线式低电压差分信号传输(BLVDS)技术。其优点是,确保利用低电压差分方式传输的信号,可获双向及多站(开岔)式配置的支持。

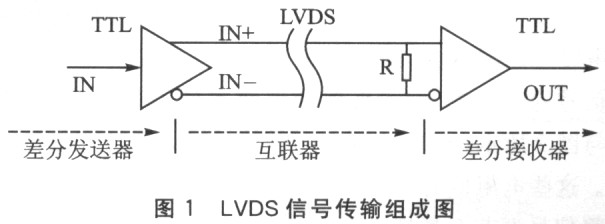

LVDS信号的传输一般由三部分组成:差分信号发送器、差分信号互联器和差分信号接收器,如图1所示。

由于LVDS技术可以支持数据的高速率传输,且功耗远比同类技术低,因此渐渐成为厂商普遍采用的差分接口标准。市场上的很多产品都需要在低功耗的 *** 作环境下进行高速率数据传输,而采用LVDS技术,可以确保所开发的产品能够支持高达数百Mbps的数据传输速率。有一点要注意的是,IVDS的出现虽然满足了短距离传输条件下数据高速传输的要求,但传统的IVDS不能支持长距离传输。具体就是,I。vDs串行/解串器接口可以驱动,但电缆的长度受到一定的限制。一般距离短至只有几英寸(芯片与芯片之问),最长则不超过几米;但目前许多系统都需要具有长距离传送数据的能力,以确保可以利用长达几百米以上的电缆传送数据。对于系统设计来说,电缆加长之后,便要解决多个长距离传送的设计问题。本文主要讨论如何扩大IVDS技术的数据传送范围,以满足长距离传送的要求。推出了ANSI/TIA/EIA一644标准的美国国家半导体公司建议的办法是,采用高速串行数字接口自适应电缆均衡器及电缆驱动器芯片。

1 传输系统结构

同轴电线和双绞线是应用很广泛的信号传输载体,同时也是有损耗的传输线。对信号的传输损耗与信号频率的平方根成正比,会使信号产生失真和畸变,引起数字码元间的串扰。因此信号在传送过程中都会出现大幅衰减,衰减程度取决于数据传输率(频率)及电缆长度。经由电缆传送的低电压差分信号也会同样出现衰减情况,因此这类信号只适用于短距离的传送。

若采用没有信号调节功能的LVDs芯片,电缆的长度一般不能超过几米;但这些系统只要采用设有驱动器预加重功能和接收器均衡功能的LVDS集成电路,电缆的长度便可最多到数百米。采用LVDS接口芯片的系统如果必须进行长距离的数据传送,便应采用专为驱动较长电缆而设的芯片,并将之搭配LVDS芯片一起使用,以便互相支持。图2所示的通信通道采用10位的LVDS串行/解串器,以及串行数字接口电缆驱动器/均衡器芯片组,驱动经同轴电缆传送的信号。

这条传输通道采用美国国家半导体10位的串行/解串器(可以有很多选择,国家半导体推出了10位/16位/18位的SerDes,Maxim也推出了自己的这类产品)以及串行数字接口电缆驱动器/均衡器芯片组(比如CLC001和CLC012,现在国家半导体又推出了一系列这类产品,如CLC005和CLC014,性能有了很大提高)。这组串行/解串器可以缩小连接器及电缆的体积,有助降低系统成本。此外,串行/解串器还可充分利用低电压差分信号传输的优点,例如卓越的抗噪声干扰能力、低功率 *** 作、低电磁干扰以及简单的终端设计。

在利用10位的LVDS串行/解串器以及串行数字接口电缆驱动器/均衡器芯片组驱动,经由双绞线电缆传送的信号的例子中,除了采用的电缆有所不同之外,这条通道与图2所示的通道只有一个区别,就是R1~R6的电阻值。这些电阻值的大小由实验决定。只要调控电阻值,便可将信号调节至最理想的均衡状态。

图2中的电缆接收器CLC001为高速驱动器,可驱动同轴电缆和双绞线。它采用差分输入和差分输出,经交流耦合驱动同轴电缆。传输的信号再经交流耦合送到自适应均衡器CLC012。同轴电缆的特性阻抗为75 Ω。输入端接人37.5 Ω的电阻,是为了平衡每一端的输入阻抗;输出端接75Ω的电阻,是为了阻抗匹配以及为输出建立合适的EcL电平。图2中的LVDS差分接收器LVl212A是一款高阻抗芯片,可以检测小至20 mV的差分信号,然后将这些信号放大,达到标准逻辑电位。由于差分信号具有1.2 v的典型驱动器补偿电压,而接收器可以接受由接地至2.4 v的输入电压,因此可以抑制高达±l V来自传输线路的共模噪声.此外,LVDS驱动器及接收器可以带电插入,因为恒流式驱动不会对系统造成任何损害。接收器的另一个优点是,具有高度的安全性,当输入引脚均处于浮动状态时,接收器的安全功能可以防止输出出现振荡。

2 自适应电缆均衡器的作用

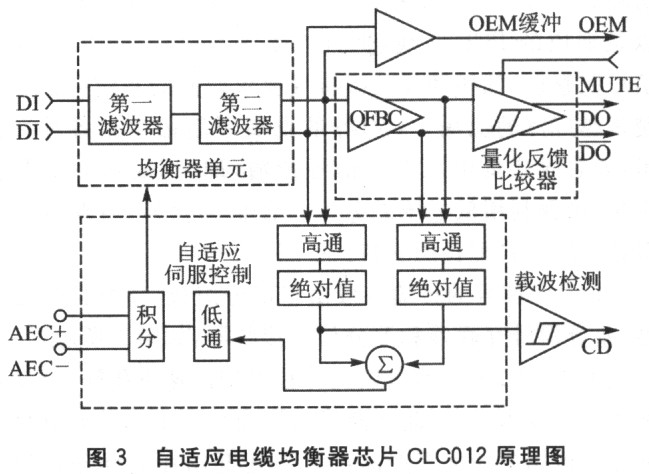

经电缆长距离传送的信号都会出现衰减现象,但只要采用串行数字接口电缆驱动器/接收器芯片组,便可避免信号衰减。Comlinear公司的CLC012是负责执行这个任务的丰要芯片,其主要工作是均衡电缆传送的信号。图3为CLC012原理图。

CLC012自适应电缆均衡器为均衡在同轴电缆和双绞线(或具有类似色散损耗特性的介质)上传输的数据提供了一个低成本的单片集成解决方案,只需使用一个芯片和很少的几个外围元件就能轻松地完成高速数据流的再生。它能自适应地对不同长度的电缆和双绞线进行均衡,均衡的长度从0 m到相当于对信号在200 MHz时衰减40dB的长度,即300m的Belden型同轴电缆或。120 m的五类未屏蔽双绞线。均衡器可对50 Mbps~650 Mbps;范围内的数据流进行均衡。

CLC012内有自适应伺服控制单元,可以产生用于控制滤波单元的控制信号。该信号是与电缆长度成正比的电压信号,这一单元接收来自滤波单元的输出信号和量化反馈比较器的差分信号,用它们来构成这一控制信号。伺服环路响应由接在AEC正端和AEC负端的外接电容控制,伺服控制电压即AEC正端和AEC负端的差分电压与传输线长度近似成正比。当这一电压值超过500 mV时,不能再提供更多的均衡。

CLC012的抖动极低,对于通过200 m同轴电缆传输的270 Mbps的数据流,其抖动的典型值为180 ps。这一优越的性能为数据链路提供了很宽的噪声容限。均衡器有二级自适应滤波器单元,对不同长度的电缆进行自适应均衡。均衡器可以使用单电源(+5v或一5.2 v)工作,功耗仅290 mW。除了上述功能外,芯片还具有载波检测输出和静音控制端。这两端接在一起时可以在没有信号输入时对输出进行静音控制。另外,还提供一个经缓冲的输出端眼图监测输出OEM,便于观察均衡效果。

在整个防止信号衰减的过程中,CLC012均衡器是串行数字接口中最重要的元件。它的任务是从表面上无价值波形中回收信号,并将它恢复到适当电压电平。这里CLC012芯片发挥极重要的作用,即使所用的电缆较长,例如长达300 m的优质同轴电缆(Belden8281)或长达120 m的5类无屏蔽式双绞线电缆(这样的长度足以令所传送的200 MHz信号出现40 dB的衰减),均衡器芯片都可自动为信号损耗提供补偿。均衡器可为电缆损耗提供补偿,使电缆传来的串行数字信号可以重新恢复其原有强度。图4以眼图(eye pattern)方式说明不同传输速率下均衡前后的效果。

3 系统设计与传输性能指标

LVDS系统的设计,要求设计者具备超高速单板设计的经验并了解差分信号的理论。对于利用LVDS串行/解串器及串行数字接口芯片进行长距离数据传送的通道来说,以下的几个建议有助提高数据传送的性能:

◆按照LVDS接收器互连线路的阻抗大小,为CLC012芯片提供适当的负载。

◆采用屏蔽双绞线电缆,以便将串音减至最少。

◆至少使用4层PCB板(从顶层到底层),即LVDS信号层、地层、电源层、TTL信号层。

◆使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上。

◆使LVDS驱动器和接收器尽可能地靠近连接器的LVDS端。

◆使用分布式的多个电容来旁路LVDS设备,表面贴电容靠近电源/地层引脚放置。

◆电源层和地层应使用粗线,保持PCB地线层返回路径宽而短。

另一点非常重要的是,差分线对要求严格的匹配,否则引起能量反射导致芯片被击穿。这点是作者在实践中付出惨重代价摸索出来的。

◆不要仅仅依赖自动布线功能,应仔细修改以实现差分阻抗匹配并实现差分线的隔离。

◆尽量减少过孔和其他会引起线路不连续性的因素。

◆使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10 mm),这样能减少反射并能确保耦合到的噪声为共模噪声。

◆使差分线对的长度相互匹配以减少信号扭曲,防止引起信号间的相位差而导致电磁辐射。差分线对内,两条线之间的距离应尽可能短,以保持接收器的共模抑制能力。在印制板上,两条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。

◆避免将导致阻值不连续性的90。走线,使用圆弧或45。折线来代替。

4 传输系统结果分析

图2所示的电路均利用相关芯片的评估套件组建,国家半导体曾利用误码率测试仪加以测试.测试用的输入信号是一条10位宽的伪随机码流(PRBS-15),并由40MHz的时钟(DS92LV1021ATCLK)加以锁定.数据传输率相当于利用200m电费传送的480Mbps传输速度.测试结果显示,这两款电路在 *** 作时并无误码出现.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)