使用一个FPGA便可实现的64通道下变频器

RF Engines公司的ChannelCore64使设计者能够用一个可对FPGA编程的IP核来替代多达16个DDC(直接下变频器)ASIC,可显著减少PCB面积,降低功耗而且增加灵活性。和原来的方法相比,新方法是降低成本的典型代表,随着通道数目的增加,降低成本的需求愈加突出。在提供灵活性和简化设计的同时,这种方法也能降低功耗。ChannelCore64的应用包括无线基站,卫星地面站和其它多通道无线电接收器等。谡庑┫低秤τ弥校?枰?右桓銎荡?浅?淼男藕胖刑崛『芏嗑哂胁煌??淼耐ǖ?或者信号),然后将整个系统的其它部分与之匹配来简化设计。

ChannelCore64

几乎所有的无线接收器都要通过下变频,从一个非常宽的输入频谱中提取一个或者多个相对窄的通道。在系统的前端,随着灵活性的增加,迫切要求不同的无线接入技术协同合作,允许对波段进行动态的可重新配置,以及对接收系统设计的投资进行前景估计。此外,用户对带宽需求的不断增加,加上诸如MIMO(多输入/多输出)等新技术的出现,要求系统必须具有支持和处理越来越多的信号通道的能力。

到目前为止,一般都是利用DDC ASIC,通常能处理达4个通道,因此,一个复杂的多通道应用就需要多个大且昂贵的系统板。RF Engines公司提出了一个新颖的通道选择架构,能够在单个FPGA器件上处理多达64个通道。这能大幅降低成本、面积和功耗,因为一个器件能够替代原先16个ASIC,尤其在信道数量增加时较传统方式更能降低成本。

ChannelCore64利用了一种独特的下变频方法,和其它基于FPGA的DDC解决方案相比,此方法能够获得很大的硅面积节省,同时还能提供各种先前基于ASIC的DDC芯片具有的配置控制选项。例如,此IP核能够很好地工作在Xilinx Virtex II Pro 30 FPGA器件上,在所有通道都有效的工作环境下,最大功耗只有4W。如果用Altera器件实现,性能大体相当。

740)this.width=740" border=0>

740)this.width=740" border=0>

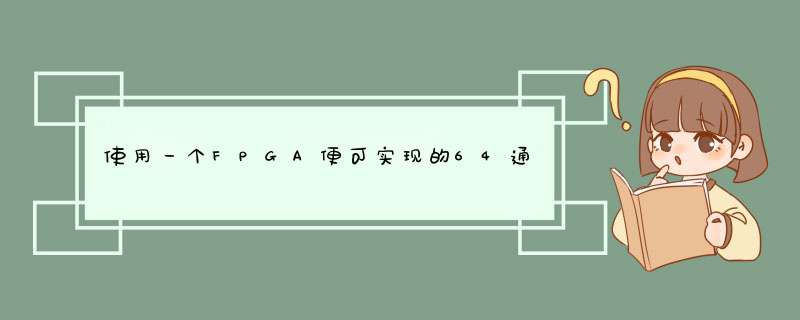

图1 ChannelCore64内部构成

此IP核(见图1)能够使用户从一个或者两个输入源独立地选择各个通道,调节每个通道的中心频率和增益,且选择不同的滤波形状和带宽采样速率以适应变化信号的工作环境。一个集成的高质量信号重采样器能够保证终端到终端的动态范围至少在80dB以上,即使对于分数重采样比例也能达到此动态范围。这要比其它分数重采样解决方案高很多。

ChannelCore64提供了8个独立的用户可编程滤波器,用户能够根据系统所需要的性能要求进行匹配。滤波器设计包括等纹波,根余弦和高斯滤波器等。这些滤波器能够工作在高采样速率下,作为重采样处理过程的一部分。能够对一个4倍的过采样输出提供相当于一个80抽头的滤波器。为了使滤波器能够提供多个可能的输出带宽,选择滤波器时应充分考虑输出采样速率。

重采样器能够对每个通道提供输出速率控制,用于匹配调制系统速率。采样速率的分辨率小于0.01Hz。对于每个通道,饱和度指示和微调增益控制的分辨率为0.01dB,各个通道完全独立,内核执行过程中在不影响其它信道工作的条件下可进行信道重构。

ChannelCore64的主要特色包括:支持两个16位ADC输入(每个采样率达140MSPS);64个独立的可连接各自ADC的下变频信道;独立的信道中心频率调谐能力,分辨率高于0.01Hz;独立的信道频宽选择功能;独立的采样率输出选择功能,分辨率高于0.01Hz。

该内核针对无线基站、卫星地面站及其它多信道无线接收机等应用。在这些应用中,MIMO技术可被很好地应用,例如用额外的天线来获得更多的信号信息,通过去除多通路效应,对大量输入信息的处理可获得较好的接收质量,因此大大提高了服务质量。通常,天线数目越多,也就意味着需要更多的ASIC,同时也就意味着成本和功耗的增加。然而,利用基于ChannelCore64的解决方案,额外的通道能够很容易地配置,例如,从24通道到64通道,服务质量大大提高了,但是成本的增加几乎可以忽略。

ChannelCore64 可以EDIF网表的形式交付,同时可以加上用户约束文件、例化模版、VHDL模型、测试文件和Matlab模型。Bit-true Matlab模型可以免费提供,允许设计者在系统环境下,精确地仿真ChannelCore64核。该核可提供简单的授权模型以及用户变量,包括上变频器,均可根据需要定制。ChannelCore64已经完成测试,证明其能提供快速的、低风险的、经过优化的解决方案。

740)this.width=740" border=0>

740)this.width=740" border=0>

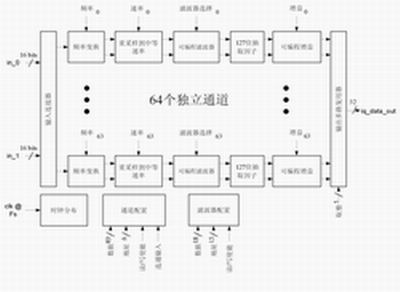

图2 ChannelCore64可在一个FPGA中

实现64个独立的下变频通道

这个64位的核能够和目前流行的A/D转换技术匹配, 能够提供通用功能来满足尽可能广的要求(见图2)。RF Engines公司正在对定制FPGA的开发进行专门研究,并且很快就能根据客户的需要提供相关的替代产品。对于一个给定的核的设计,其最主要的可变设计参数包括: 数据和可编程界面, 频率和数据率精度, 滤波器参数和无杂散动态范围。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)