在应用DSP进行数字信号处理时,通常都要用采样电路对模拟信号进行采样,然后进行A/D转换器转换成数字信号再进行数据处理。这里给出一种由TLVl571与TMS320VC5410组成的信号采集系统。

1 TLV1571简介

在DSP的外围电路中,A/D转换器比较重要。基于不同的应用,可选择不同性能指标和价位的芯片。一般的A/D转换器的选择主要考虑:转换精度、转换时间、转换器的价格。

这里选择了TI公司专门为DSP配套的一种10位的并行A/D转换器TLVl571,该器件给定的CLK频率达到的等效最大采样频率为(1/16)fCLK。

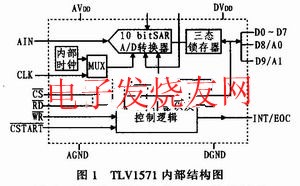

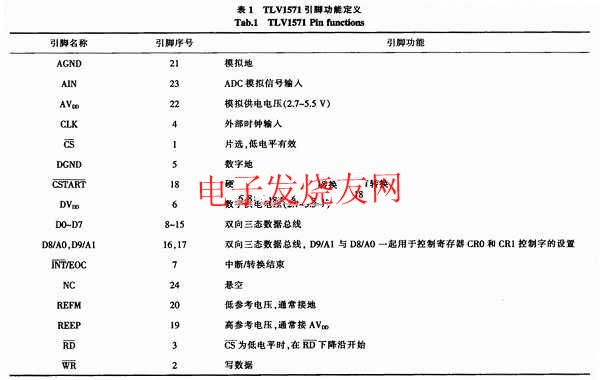

1.1 TLVl571的内部结构及引脚定义

TLVl57l的内部结构及引脚功能定义如图l及表l所示。

TLVl57l采用2.7~5.5 V的单电源工作,能接受0~3.3 V的模拟输入电压。此时以625 Kb/s的速度使输入电压数字化。在5 V电压下,以最大1.25 Mb/s的速度使输入电压数字化。该A/D转换器具有速度高,接口简单以及功耗低等特点,成为需要模拟输入的高速数字信号处理的理想选择。

1.2 TLVl571的初始化

1. 3 TLVl571的控制寄存器控制字的设置

TLV1571的控制寄存器格式如表2所示,它可以实现软件配置,其两个最高有效位D9和D8用于寄存器寻址,其余的8位用作控制数据位。在写周期内所有 寄存器位同时写入控制寄存器,用户可配置两个控制寄存器CR0和CR1,对于控制寄存器0(CR0),A1:A0=00,其配置如表3所示;对于控制寄存 器1(CR1),A1:A0=01,其配置如表4所示。

通过改变控制寄存器的控制字,可以选择TLVl571的工作方式。通过配置CR0.D5可以选择时钟源,对于时钟源的选择,有内部时钟和外部时钟,它的内部具有10 MHz振荡器。通过配置CR1.D6可以选择内置振荡器的工作速度,配置为(10±1)MHz或(20±2)MHz。输出方式也有2种方式:二进制输出和补码输出。

在单通道输入方式下则CR0.D3=0,CR1.D7=O;采用软件启动方式则CR0.D7=1;采用内部时钟源则CR0.D5=0;内部时钟源振荡频率设置为20 MHz则CR1.D6=1;采用二进制输出方式,则CR1.D3=0。所以最终得到的控制寄存器控制字为:CR0=00COH,CR1=0140H。在单通道软件启动时.最初由

的上升沿启动采样,在

的上升沿发生采样:在采样开始后的6个时钟周期后开始转换,INT方式时,每次转换后产生一个

脉冲;EOC方式时,转换开始,EOC由高电平变至低电平,转换结束后换回高电平。

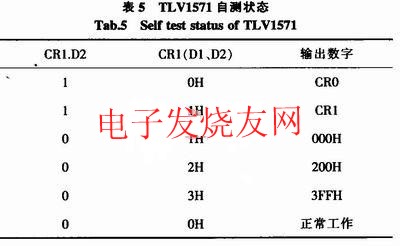

1.4 TLV1571的自测

TLVl571提供了3种自测方式。当采用这些自测方式的时候,不用提供外部信号便可检查A/D转换器本身工作是否正常。通过写CR1(D1、DO)来控 制这3种自测方式,具体方法如表5所示。另外当CR1.D2=1,CR1(D1、DO)=0时,此时回输出写入CR0控制寄存器的控制字;当CR1.D- 2=1,CR1(D1、DO)=1时,此时回输出写入CR1控制寄存器的控制字,也可以用来测试和检验控制字是否正确写入控制寄存器及A/D转换器是否正 常工作。

2 的接口连接及调试

2.1 TLVl571与TMS320VC5410的接口

TLV157l与TMS320VC5410的接口连接很简单,如图2所示。这个系统中没有采用硬件启动采样控制的方法,而是采用了软件启动的控制方法。时 钟信号也是采用A/D转换器的内部时钟。如果需要外部时钟输入,可以由DSP提供一个精确而且可以根据需要控制变化的时钟信号。本设计采用查询方法来读取 转换后的数据。另外在设计电路时要注意,当供电电压为3 V时,TLVl571提供的采样速度是625 ks/s,此时它的功耗为12 mW;当供电电压为5 V时,它提供的采样速度是1.25 Ms/s,功耗为35 mW。

2.2 系统的调试

在调试这个系统时,由于DSP外部的I/O空间的调试,基本上只涉及如何选通该空间,如何从外部空间取数据或读数据,如何和外部空间建立 握手信号,但是要注意的是DSP与外围器件时序上的配合。特别是对于数据线信号的读取,当系统中有多个器件共享DSP数据线的时候,一定要处理好各个器件 的时序配合。使处于非工作状态的器件的数据线处于高阻状态,以免影响正常工作的器件的数据读写。在对TLV-l57l调试过程中需要注意以下问题:1)必 须将TLVl571的2个状态字正确地写入到A/D,可以在写入后读一次数据来确认写入数据的正确性,也可以采用循环写入方式利用示波器观察写入的两个脉 冲信号,另外也可以用读出写入CRO、CR1控制寄存器控制字的方法来判断控制字是否正确写入了TLVl571的控制寄存器内,也可以判断器件是否正常工 作;2)TMS320VC5410的读写信号只有一根地址线,所以需利用XF引脚控制TLVl57l的读信号,且必须在DSP每次读入数据后,用软件控制 XF引脚输出信号到TLVl57l,否则A/D将不再采样。另外如果采用DSP定时中断来读取数据的时候,在设置定时中断时,中断间隔只要大于 TLVl571工作频率所需采样周期数,可以不用查询的方法来读取EOC信号,而是直接读取采样数据,然后控制XF输出信号使它进行下一次采样工 作;3)TLVl571不能采样负的电压信号,如果必须采样负的电压信号,可以人为引入一个直流信号,将负电压抬高到正电压,而DSP要在采样信号中减去 引入的直流信号;4)为了验证采样信号是否正确,可以在CCS下画出所采样数据的时域图或频域图。

3 结束语

实验证明该系统可以满足一般高速实时信号的采样和处理工作,验证了在单通道下该系统可以达到最高1.25 Ms/s的采样速度,而且通过调整DSP定时中断时间可以方便的获得在该系统最大采样频率(1.25 Mb/s)以下的各种采样速度,可以灵活的满足多种应用。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)