何为时序,时序就是CPU在各引脚信号在时间上的关系

何为总线周期,总线周期就是CPU完成一次访问内存或接口 *** 作所需要的时间。

1个总线周期至少包括4个时钟周期(时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。时钟周期是一个时间的量。时钟周期表示了SDRAM所能运行的最高频率。更小的时钟周期就意味着更高的工作频率。)

8088的系统总线介绍:

1.总线:是一组导线和相关的控制、驱动电路的集合。是计算机系统各部件之间传输地址,数据和控制信息的同道。

包括:地址总线(AB),数据总线(DB),控制总线(CB)。

2.总线的分类:

①按相对CPU的位置分为:片内总线,片外总线。

②按层次结构分:CPU总线,系统总线,外部总线

3.总线的系统结构

单总线结构:

多总线结构:

面向CPU的双总线结构:

面向存储器的双总线结构:

现代微机中的多总线结构:

4.总线的基本功能

数据传送,仲裁控制,出错处理,总线驱动。

5.常用的系统总线

①ISA(8/16位)

②PCI(32/64位)

③AGP(加速图形端口,用于提高图形处理能力)

④PCI-E(PCIexpress):目前最新的系统总线标准,采用串行方式传输数据,依靠高频率来获得高性能。

6.总线的性能指标

①总线带宽(B/S):单位时间内总线上可传送的数据量

②总线位宽(bit):能同时传送的数据位数

③总线的工作频率(MHz)

总线带宽=(总线位宽/8)X(总线工作频率/每个存取周期的时钟数)

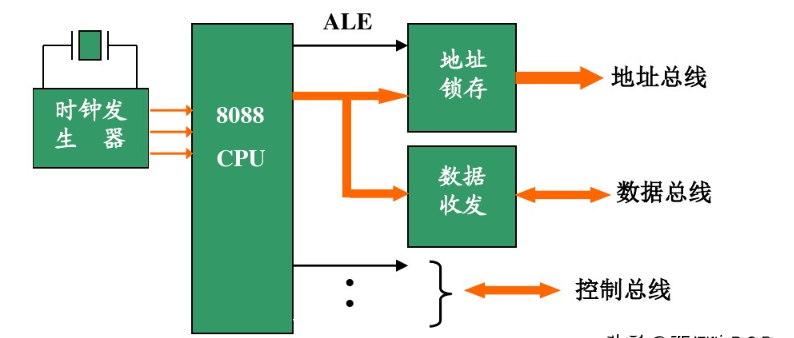

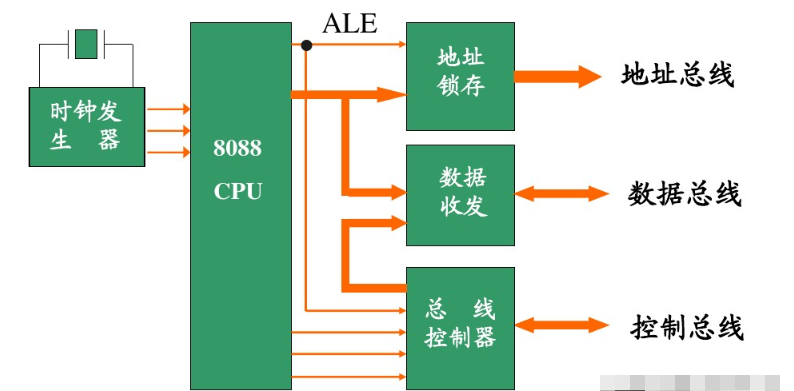

7.两种工作模式下总线连接

8088可工作于两种模式下

①最小模式为单处理器模式,控制信号较少,一般可不必接总线控制器

②最大模式为多处理器模式,控制信号较多,须通过总线控制器与总线相连。

最小模式下总线连接示意图:

最大模式下总线连接示意图:

责任编辑人:CC

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)