用FPGA实现音频采样率的转换

如今,即使低成本FPGA也能提供远远大于DSP的计算能力。目前的FPGA包含专用乘法器甚至DSP乘法/累加(MAC)模块,能以550MHz以上的时钟速度处理信号。

不过,直到现在,音频信号处理中还很少需要用到这些功能。串行实现千赫级音频算法使用的资源与数百兆赫级信号处理所需的完全相同。

因此,像PLD和FPGA这类可编程逻辑元件很少用来处理低频信号。毕竟,与基于传统DSP的实现相比,用硬件并行处理数??算无益可言;对于如此低的采样率,大多数串行DSP实现都是绰绰有余。其实,音频应用所含乘法运算之多曾使其只能使用很大的FPGA实现。因此,用DSP实现低采样率音频应用曾经比使用大型FPGA更有效――成本较低,而且有成熟的软件支持。

Synplicity公司最近推出的Synplify DSP综合工具可以将具有大量乘法运算和低采样率的算法有效地映射到FPGA中的专用DSP模块上。该工具基于MathWorks公司推出的十分普及的 MATLAB和Simulink工具。

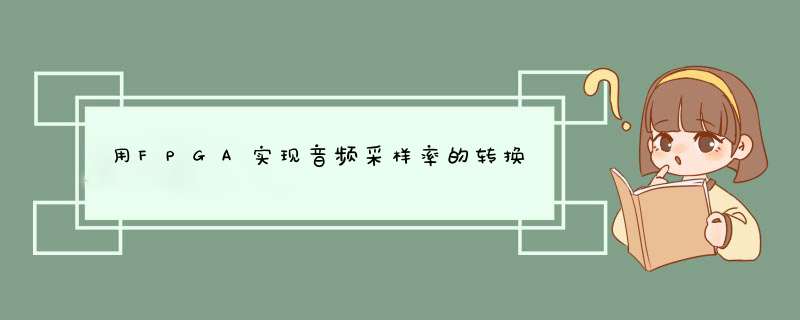

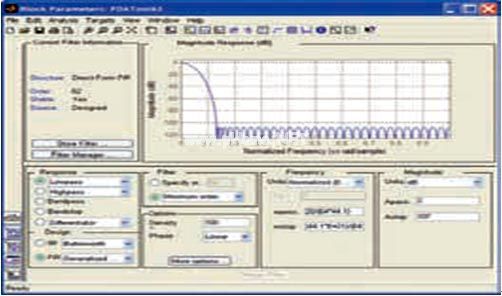

算法先用专用模块集或专有的“M”脚本语言描述定义,然后转换成RTL硬件描述语言。该模块集允许单速率和多速率实现。它不仅能生成VHDL和Verilog代码,还可以处理定点量化、流水线和环路展开这类任务,并且能连接到 Simulink开发环境中的模块集进行仿真(见图1)。

图1:在 MATLAB/Simulink中实现、量化并验证模型。Synplify DSP工具可以将模型转换成RTL代码,并针对空间或速度对这些代码进行优化。

应用示例:采样率转换

下面以音频采样率转换器作为实例加以说明。这种转换器可以将信号从一种采样率转换成另一种采样率,而对信号的影响极小。处理具有不同采样率的信号时需要用到这种转换器。

例如,光盘的采样率是44.1kHz,而数字音频磁带的采样率通常是48kHz。由于存在数据格式转换,用新采样率播放源数据就不够了。以数字音频磁带使用的采样率播放光盘资料会引起失真。因此,必须对采样率加以转换。

处理音频信号时使用的采样频率有多种,常见的有 44.1kHz、48kHz、96kHz和192kHz。转换过程必须慎重,务必保持0-20kHz可闻频率信号的完整性。应保持信号所含信息的变化最小,以免音质下降(图2)。

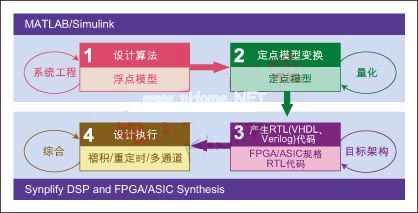

图2:用Synplify DSP模块集和Simulink FDA工具提供的模块实现采样率转换器。用Simulink模块集元件进行验证。

显然,用FPGA实现音频频率的采样率转换器存在以下问题:

1. 算法问题:

a. 可能的最高信噪比

b. 原始信号所载信息的可能最小变化

c. 算法的有效描述,因为FPGA中的资源消耗在很大程度上取决于描述的质量

d. 量化

2. 实现问题:

a. 逻辑正确的算法实现

b. FPGA资源限制

c. 速度优化实现

d. 延迟

转换需要较高的时钟速度,因为具体实现取决于对转换信号的足够过采样。FPGA系统时钟频率与待转换信号的频率差异必须相应较大。

FDA 工具可帮助生成和验证各种FIR和IIR滤波器。该工具是Simulink信号处理工具箱的组成部分,Synplify DSP就是使用此工具箱实现滤波器结构

对于CD质量的音频信号,还要求信噪比不得低于100dB。专业应用甚至需要大于 120dB的音频信号。就信号质量而言,其他低频信号(如控制电路算法)远不如音频信号那样苛刻。

算法

多相FIR滤波器结构需要转换采样率(异步重采样)。算法包括两步,第一步是频率过采样,第二步是线性插值,这是从给定频率生成不同频率时需要的。这两个频率相互异步。

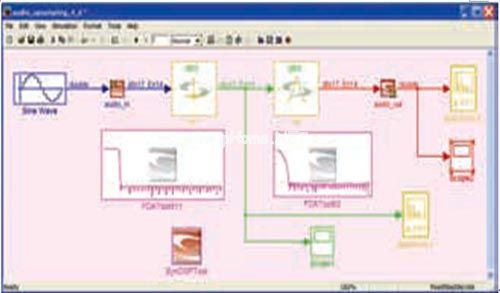

以单步方式进行信号重采样所需资源较多,因为滤波器会较复杂。这种实现需要数百万次乘法运算。这样的描述效率很低的,应当加以避免。如果线性插值在第二步实现,那么结构就会简单得多(图3)。

图3:分两步实现采样率转换器(一、过采样;二、线性插值)以提高效率。

高效地描述过采样(第一步)是让 FPGA实现节省资源的唯一方法。如果用若干级联级而非单一运算步骤来实现这部分电路,所需运算数量就会大大减少。

在算法实现时,必须确定执行运算的目标架构(DSP或FPGA)。与具有固定架构的数字信号处理器不同,FPGA可实现任何架构。不过,当实现大量单独的乘法运算时,FPGA最终会受到器件尺寸的限制。

所需乘法器的数量将随着滤波器抽头的增加而增加。每个抽头都需要使用一个DSP模块或乘法器。当级联重采样电路时,各滤波器必须执行复杂程度很低的功能。从理论上讲,单独的级越多,滤波器的实现就越好。

减少运算次数之方法的数学推导在技术文献中已有广泛论述。实践结果表明,尽管有必要级联滤波器电路,但必须对级联的数数加以限制。如果使用级联级数过多,就可能超过实现设计的可用资源。如果用FPGA作为目标架构,实践证明两级电路最好。

整个电路由用于过采样的两个相对简单的滤波器和一个简单的线性插值器组成。这种结构可以有效地映射到FPGA。

设计实现

可以在Simulink中用Synplify DSP模块集和Simulink的滤波器设计与分析(FDA)工具实现该电路。FDA工具可帮助生成和验证各种FIR和IIR滤波器。该工具是Simulink信号处理工具箱的组成部分,Synplify DSP就是使用此工具箱实现滤波器结构。

Synplify DSP模块集或FDA工具提供的所有电路元件在PorTIN和PortOUT描述之间都有定义,它们能够生成VHDL或Verilog代码。 Simulink模块集中的FFT和SCOPE元件对动态响应进行频谱分析和验证。这些模块专门用于功能验证,包括浮点到定点转换功能(量化)。这些模块都不用硬件实现。

算法实现的第一部分包括两个FIR滤波器:第一个滤波器有512个抽头,第二个滤波器有6?个抽头。因此,由过采样生成的RTL代码共含有576个乘法运算,这正是使用FPGA显得并不具有商业可行性的原因。这么大的FPGA会受到成本制约,因为需要用到有 6?0个DSP48模块的特大型Xilinx Virtex-5 XC5VSX95T器件。

未映射到专用硬件结构(DSP模块)的所有乘法运算都必须用通用逻辑资源(LUT或寄存器)构建。这样会导致资源要求上升而最高时钟速度下降。与通用逻辑单元相比,专用的DSP48模块作为乘法器会有效得多(图4)。

图4:用Simulink的滤波器设计与分析(FDA)工具实现滤波器。

设计优化

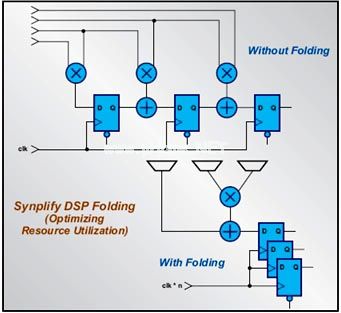

Synplify DSP的折叠选项可用来尽量减少所用乘法器的数量。在低采样频率下工作的电路尤其可从这一优化中受益。

其原理很简单。通常,每个乘法运算使用一个硬件乘法器,即使对于千赫级采样频率也是如此。然而,FPGA能以数百兆赫级的时钟速度工作。如果硬件乘法器在FPGA的系统频率下工作,就可以用时间多路复用过程按时序处理乘法运算。

假设电路的采样频率是3MHz,而FPGA最高可以在120MHz频率下运行。如果以系统频率运行乘法器,则每个硬件乘法器可以执行40次运算。此时所需硬件可以减少40倍。也就是说可以将上述采样率转换器(或使用低采样频率的任何其他电路)“折叠”到仅需要很少硬件乘法器的程度。所以,也可以在现有最小的低成本FPGA中实现这种转换器,从而真正取代DSP。

当然,还可能将计算量特别大的算法从DSP卸载到FPGA,从而减轻处理器的负荷。如果您的DSP应用已经超过性能极限,而且您已经为针对特定DSP架构的应用源代码作出大量投入,那么这种方法尤其有用(图5)。

图5:可以用折叠功能显著减少所需的FPGA资源。

因为Synplify DSP中的折叠功能还支持多速率系统,所以与只有一种采样频率的系统相比,您可以进一步减少所需乘法器的数量。过采样使用两个FIR滤波器完成。这两个滤波器以不同的采样频率运行。以较高采样频率运行的滤波器可以用您指定的折叠系数进行折叠。

以较低采样频率运行的滤波器用相对较高的系数折叠。获得此系数的方法是用两个滤波器的采样频率之差乘以折叠系数。例如,如果一个滤波器的采样频率是另一滤波器的8倍,则较快的滤波器用系数 8折叠,而较慢的滤波器用系数6?折叠。

这样甚至可能生成以通常不能折叠的很高采样率运行的空间优化电路。例如,如果系统以 200MHz采样率运行并使用折叠系数2,那么系统频率就可以提高到400MHz。

您还可以将折叠系数定义为1。以最高采样率运行的电路元件不折叠。但是,以较低采样频率运行的多速率系统的所有电路元件都可从折叠和空间优化实现中受益。您只需将系统作为整体为其定义折叠系数即可。然后,折叠会自动传播到所有采样频率。

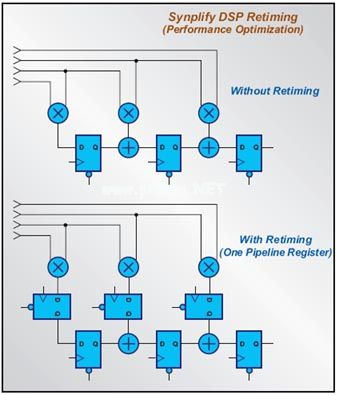

可以把折叠功能与另一优化功能-重定时功能结合起来使用。如果系统不满足目标频率要求,可以增加流水线级数,直到获得所需速率。这种做法对于使用高折叠系数的电路尤为重要,因为这类电路需要以相对较高的系统速度工作。

您还可以为折叠很少或没有折叠的电路使用重定时,除非已经达到FPGA的性能极限。可以通过增加流水线级数来减少两个寄存器之间组合逻辑门的数量(逻辑级数),这样可以提高系统时钟速度。

在生成RTL代码时,Synplify DSP工具将进行时序分析,它会考虑所需的采样频率、折叠系数和FPGA的目标架构。例如,与在较慢的低成本Spartan-3A DSP FPGA中实现的完全相同的电路相比,可以使用较少的流水线级数优化映射到快速Virtex-5 FPGA的电路。

可以用 FPGA提供的大量寄存器进行这种优化。寄存器可以大量使用,不像乘法器或LUT(查找表)那样很快会用光,这意味着可以使用寄存器轻而易举的显著提高系统时钟速度。

当然,增加流水线级数会增加系统延迟。例如,如果使用重定时系数8,计算结果就会迟8个系统时钟周期(不是采样频率周期)出现在FPGA的输出上。向系统中嵌入电路时必须考虑到这一点(图6)。

图6:可以使用重定时功能为电路定义允许的最大延迟。然后由Synplify DSP自动增加流水线级数,直到获得所需频率。

特别重要的是,务必确保上述优化不会影响Simulink中描述的原始MATLAB模型。通过验证可以对算法进行鉴定,并且对量化效应的影响予以表述。Synplify DSP软件模块集允许使用截断(去除无关位)、四舍五入(在下溢情况下)或饱和(在上溢情况下)进行从浮点到定点的转换。一旦仿真显示算法工作正常,即可生成RTL代码。优化VHDL或Verilog代码可能改变延迟,但不会改变电路的 *** 作。

本文小结

Synplify DSP工具基于MathWorks公司推出的行业标准MATLAB/Simulink软件。模块集提供的标准元件库可用于实现复杂算法。除了加法、增益和延迟等基本元件,该库还包含FIR或IIR滤波器等许多复杂功能和CORDIC算法。所有功能(包括高度复杂的FFT或Viterbi解码器)均可任意参数化。还可以创建用户定义库,或者将现有的VHDL或Verilog代码集成到Simulink模型中。

用Synplify DSP可以实现单速率和多速率系统。使用折叠、多通道化或重定时功能可以针对尺寸或速度优化代码。生成的RTL代码都是未加密的通用代码,可以使用常用工具进行综合。

为了用FPGA取得最佳结果,Synplicity推荐使用Synplify Pro综合工具。目前针对ASIC的开发环境也已经推出。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)