1 引言

在现代数字信号处理系统中,采用Flash做为DSP程序加载和引导是一种常用的方法,它为用户对那些将来可能需要改变数据或代码的系统维护提供了有效手段。利用Flash器件,能够实现在线程序编写,减少EPROM程序烧写带来的麻烦。

2 Flash AM29LV800B简介

Flash存储器又称闪存,它结合了ROM和RAM的特点,不仅具备电子可擦除可编程(EEPROM)功能,而且不会断电丢失数据同时能快速读取数据,它具有在线电擦写、低功耗、大容量、擦写速度快等特点,属于EEPROM的改进产品。

2.1主要性能

AM29LV800BB-90EC是AMD公司AM29LV800B系列的一种器件,其主要性能如下:访问时间:90 ns;存储容量:8Mbit;工作温度范围:-55~+125℃:在线编程电压:3.0~3.6 V;低功耗:读 *** 作时电流为7 mA,编程/擦除时电流为15 mA。

2.2引脚功能说明

A0-A18:19根地址线;

DQ0-DQ14:15根数据线;

2.3工作模式

2.3.1读模式

为了读取数据,系统需将CE和OE设为低电平,同时将WE设为高电平。在器件上电或硬件复位后,器件默认设置为读模式。

2.3.2写模式

为了向器件写入数据或指令,系统需将CE和WE置为低电平,同时将OE置为高电平,写 *** 作需要4个周期,前3个周期向两个特定地址写入3个特定字符,第4个周期将所需数据写入相应地址:

2.3.3复位

向器件的任意地址写入特定指令,该器件复位,复位后默认为读模式。

2.3.4自动选择模式

向器件两个特定地址写入3个特定的字符,该器件就进入自动选择模式。在该模式下获取器件的厂商号和设备号,系统必须通过复位指令断开。

2.3.5擦除模式

片擦除是一个6周期 *** 作,需向两个特定地址写入4个特定字符。

3 DSP与Flash接口设计

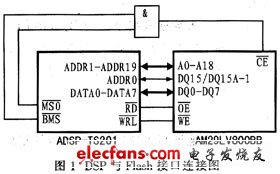

ADSP-TS201是ADI公司的TIgerSHARC系列处理器的一种器件,其内核工作频率可高达600 MHz,指令周期为1.6 ns,片内存储器DRAM为24 Mbit,集成I/O接口,包括14通道的DMA控制器,4个链路口,可编程标志引脚,SDRAM控制器,外部端口,2个定时器等,具有IEEE 1149.1兼容的JTAG端口用于在线仿真,灵活的指令集和支持高级语言的DSP结构便于DSP编程。

ADSP片内无ROM,不能将应用程序和数据直接存储在DSP内部,通常需将应用程序存储在外部存储器。系统工作时,通过加载 *** 作将应用程序载人到DSP内部执行。由于EPROM空间只提供8位数据线,因此如果Flash是16位甚至更高位,那么Flash应当配置成8位工作。由于EPROM接口是专门为处理器采用EPROM或者Flash进行程序引导而设计的,而EPROM和Flash的数据传输并不是高速的,因此为了保证通用的EPROM和Flash能正确引导处理器运行程序,ADSP-TS201在进行每次EPROM读 *** 作时需插入16个等待周期,并且在最后一个EPROM引导总线周期后有3个等待周期,用做EPROM的断开时间。ADSP-TS201提供BMS引脚用于引导存储器选择,作为Flash的片选信号,实现系统加载。此时TIgerSHARC只能通过特定的DMA通道0将程序从EPROM自动加载到TIgerSHARC内存,并且外部总线自动将字节数据打包成32位指令。另外TS201提供/MS0和/MS1引脚,用于存储器选择。当DSP分别访问存储器bank0或bank1时,MS0或MS1有效。该引脚也可用作Flash的片选信号,以实现Flash的在线编程。按此方式实现硬件,可采用处理器内核或者非EPROM类型的DMA方式访问Flash,但是处理器不会自动完成32位字和8位字的打包和拆包,需要编写专门的打包程序,这点尤为重要。其原理如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)