使用PLD应对产品上市时间和设计灵活性的限制

变化迅速的市场需求驱使越来越多的系统设计者在他们的嵌入式解决方案中使用PLD来缓解产品上市时间的压力以及设计灵活性需求。该市场传统上由ASSP和ASIC所主宰。而PLD过去一直被认为是高成本、高功耗的方案。但是,随着摩尔定律的继续生效使PLD的单位成本不断下降,在诸如通信、计算、外设、工业、医疗、消费和汽车等大批量应用中,PLD的灵活性、可编程性和加快上市的固有优点成为可行的ASIC和ASSP替代方案。而且硅工艺和设计优化使PLD可用于广泛的低功耗应用。

上市时间与设计灵活性

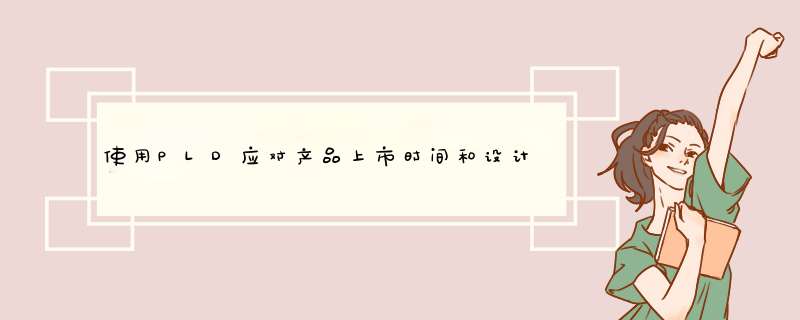

随着市场需求迅速变化,产品快速上市显得比过去更加关键。最可行的解决方案是缩短开发周期以缓解上市时间的压力。可编程逻辑可使设计者达此目的。图1以基于两者的产品开发周期的比较,说明PLD产品如何有助于新产品的引入。

另外,由于产品生命周期的缩短,ASSP的固定功能特性无法满足产品变化的需求。越来越多的设计者在他们的产品中使用可编程逻辑,通过修改PLD设计和重构器件执行新的 *** 作以开发新功能和标准品。使用可编程逻辑,设计者可以在引入产品时提供几个不同的版本,以及能在现场对产品进行任意的更新,而无需额外的工程计划并能降低成本。

生产成本

一般会使用PLD来实现产品原型,然后用ASIC进行量产。然而ASIC开发过程需要很长的开发周期和非常高的一次性工程费用(NRE)。因此,问题就变成到底是用ASIC的投资回报好还是用PLD的投资回报好。(90nm或更先进)工艺的进步使得PLD制造商缩小了与ASIC之间的大批量价格差距。10万片及以上的128个宏单元或更小的超低密度PLD的批量单价大约为1.5美元。

使用CPLD和FPGA进行设计需要考虑静态功耗和动态功耗。在大多数电池供电的应用中,为了延长电池的寿命,待机或静态电流是最关键的参数。大多数应用中,瞬态大电流只是短暂的(例如用手机交谈时)。而大多数时间内处于待机状态的手机几乎不消耗电能。在系统中进行设计优化可以进一步降低功耗。

图1:产品开发周期

低密度、低功耗CPLD

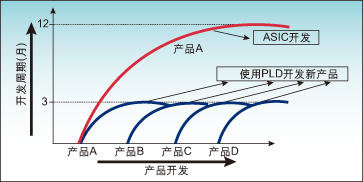

对于较小的设计,例如总线接口、桥接和手持设备(见图2),使用低功耗、基于闪存的CPLD能提供更低成本的低到超低密度的解决方案。

对于功耗敏感型应用,LatTIce半导体公司的ispMACH4000Z(Z表示零功耗)CPLD能提供相当好的低功耗解决方案。

图2:用LatTIce ispMACH4000Z进行PMP设计

由于可从多个供应商那里选择众多的器件,因此完全理解设计需求变得尤为重要。下列准则有助设计者选择合适的CPLD:

1. 静态和动态功耗的预算是多少?

3. 该应用的最佳密度和封装是什么?

4. 输出所需的电压容差是多少?

5. 所需的时序裕度是多少?

6. 所选的器件是否现场可编程的,以及开发工具是否容易使用?

7. 有哪些安全性的要求?

不同CPLD供应商有不同的规范和要求,因此选择合适的器件取决于哪些参数对设计是关键的。表1为该器件为匹配设计要求而提供的一组规范。

表1

中密度PLD设计的低功耗解决方案

高密度设计需要基于查阅表(LUT)的PLD,例如FPGA或者交叉式PLD器件。这些器件能够提供更多的嵌入式的功能、更大的存储器、更高速度、用于时序管理的PLL和DLL、DSP以及串行连接。采用LUT结构,FPGA可以满足这些设计要求,提供更大的设计灵活性。

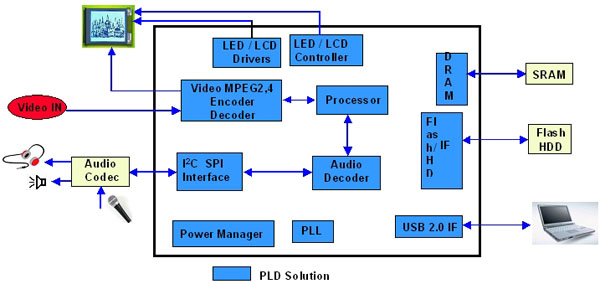

大多数基于LUT的FPGA没有“零功耗”选择。但是系统设计者可以在系统的某些工作周期中关闭器件以降低功耗。图3给出了非易失FPGA的快速电源冷启动是如何降低总功耗的。上电之后能迅速地获取逻辑功能的非易失器件对这些应用是理想的。另一方面,基于SRAM的FPGA耗费大部分工作周期用于配置。

图3:用非易失FPGA在工作周期中降低功耗

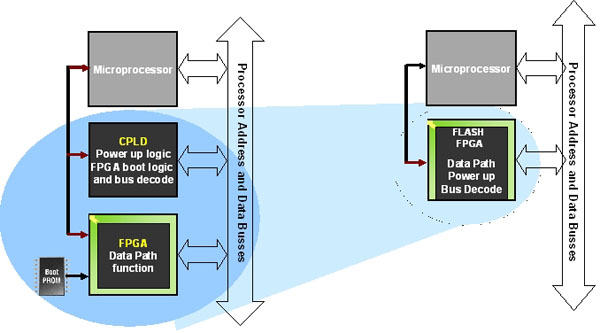

大多数FPGA是基于SRAM的,但是现在已有基于闪存的非易失FPGA。非易失FPGA比基于SRAM的FPGA更具设计优势。(参见图4)除了管理电源的功能之外,非易失FPGA的优点还包括:

1. 无需引导PROM,减少了材料清单(BOM)中的器件;

2. 无需位流,提供最高的设计安全性;

3. 实时的系统内可编程性具有调试和更新能力;

4. 无限重构的SRAM FPGA结构。

图4:非易失FPGA

LatTIce半导体公司的交叉式可编程器件MachXO就是一个很好的例子。相对传统CPLD来说,MachXO器件兼有FPGA和CPLD的非易失、低成本、瞬时上电的高性能逻辑解决方案的优点。

本文小结

由于具备上市时间优势、灵活性、可编程性和低功耗选择,CPLD和 FPGA在迅速变化的市场中成为广泛应用的可行的设计解决方案。具多种密度和多样嵌入功能特色的PLD能为设计提供快速开发周期。正如文中所述,它们能够针对低功耗和系统的高度整合进行设计优化。随着工艺的不断改进,ASIC与 PLD之间的价格也正迅速接近。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)