本文选用FPGA实现数据处理、逻辑控制,充分利用PC机,结合Labwindows图形化上层应用软件界面生成的虚拟测试系统具有较强的竞争力。本系统在FPGA单板单片主控器件控制下,实现两路独立、幅值可控的信号发生器,一路虚拟存储示波器,具有外部触发信号和采样时钟的16路高速逻辑分析仪。

硬件设计

2.1硬件系统框图

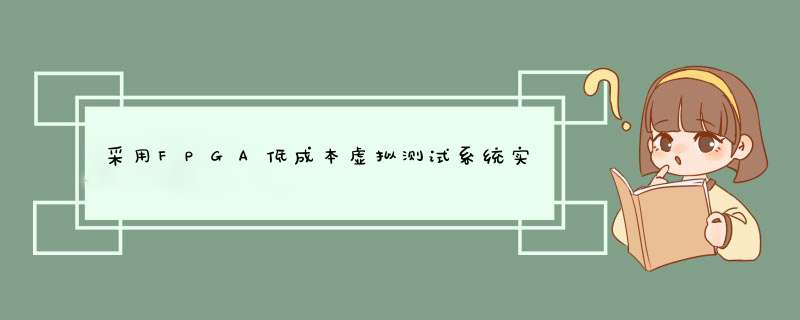

硬件系统设计是以并行处理能力强、可重配置的低端FPGA单片EP1C6为主控器件。图1所示为硬件系统框图,是由参考电压及选择模块、USB2.0接口模块、电源设计模块、高速存储模块、示波器调理输入A/D转换模块、逻辑分析仪匹配输入比较模块和信号源输出滤波模块组成。

USB2.0接口模块用于配合应用软件接受上位机命令及返回采集数据。采用Cypress公司的CY7C68013 USB2.0设备器件,该器件内部增强型8051控制数据传输。通过下载固件代码配置8051,使设备器件对主控FPGA动作模拟为片外从属FI-FO,减少FPGA设计难度。电压参考选择模块可为信号源D/A、比较器和示波器A/D提供参考电压。考虑到多种测量功能间的切换及同时工作的可能,采用两路参考电压输出和参考电压通路选择模块实现双路信号源独立工作、单路信号源协同示波器工作、单路信号源协同逻辑分析仪工作等模式。

2.2双路信号源设计

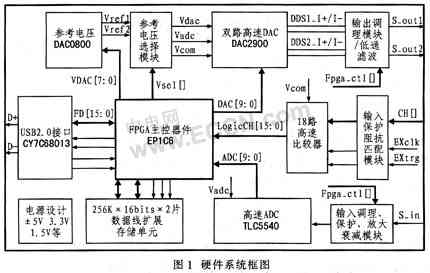

利用FPGA内部M4K存储模块、逻辑资源和高频时钟,以DDS/控制模块+高速D/A实现双路信号源,避免采用专用DDS器件,从而节省成本,提高功能的多样性。双路信号源电路设计的前端模块包括DDS方式实现的可变幅度、相位的正弦波以及硬件语言表述的占空比可调的方波、三角波、调制波形等数据输出;后端包括有高速D/A转换器DAC2900 (如图2所示)和信号调理电路组成的模数转换模块(如图3所示),其中调理模块主要由强驱动模块和35 MHz截止频率的3阶π型低通网络组成。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)