在向先进工艺技术发展的过程中,半导体公司除需满足不断增长的制造要求之外,还要面对日益增长的实现芯片设计一次性成功的压力。晶圆厂期待设计符合那些面向先进工艺节点的可制造性设计(DFM)和良率导向设计(DFY)的日益复杂的规则和建议。就设计师而言,他们希望最大限度地缩小保护频带(guardbanding),同时实现最优性能。

制造复杂性的提高给生成过孔、处理紧密排布的走线以及控制更严重的纳米几何规格效应带来了更大的难题。由于这些越来越艰巨的互连设计挑战,对于先进的工艺节点,半导体公司得到的良率一般在40%~70%之间,这样,仅良率损失一项就达数百万美元。对IC设计团队而言,这些更高的要求使之呼吁一种更加协作的方法。的确,设计和制造可以同时从最新的“DFx”(DFM、DFY和可靠性设计)优化方法中实现互利双赢。

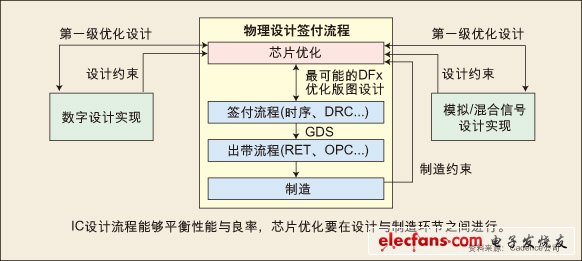

这种平衡的互连优化方法在传统布局和布线流程之后进行,可以在满足电气约束规则和制造规则的同时,提高良率、可制造性,并改善设计过程中的时序收敛问题。

目前可获得的最佳DFx流程结合了当今综合、布局和布线解决方案中有DFM意识的特性与后布线(前GDS)互连优化步骤。

应该

确保整合进设计意图(如关键的节点信息),以避免在增强DFx之后出现信号完整性(SI)和时序问题。特别要注意:通过锁定关键节点并围绕它们建立起一个保护圈,来保护它们。这个保护圈可以表示为同一层或整个层堆叠设定的保护性“禁止入内”的间距值。

在增强DFx期间执行电气认知/修正分析,以确保不违反时序和信号完整性原则。这种方法可以在DFx优化后实现收敛,并确保在流程的早期实现设计的保护频带不过宽。

合理安排DFx增强顺序。合理地安排顺序将有助于产生最佳效果,因为每一步都会为下一步打下基础。例如,从时序/信号完整性和DRC干净块开始,然后应用过孔减少技巧,接着进行布线扩展(wire spreading)、冗余过孔插入和闭合增强。

像对待时序收敛一样对待DFx收敛。建议在设计周期的早期对每一个电路执行这一原则。如果可能的话,将DFx增加到整个流程中。单元良率问题可以在综合和布局流程的早期得到解决。在布线时,可以使互连更加便于光刻、OPC和DFx。最后,利用基于空间的建模等先进方法,对布线数据进行进一步的DFx和光刻增强。

采用下一代方法,如不受网格限制的基于空间的工具,来进行最佳的DFx增强。

图:IC设计流程能够平衡性能与良率,芯片优化要在设计与制造环节之间进行。

不应该

低估互连优化的重要性。除减小保护频带以及提高芯片性能之外,互连优化还可以加快量产速度,甚至可将良率提高6%,从而带来可量化的收益。良率每提高1%,就可节省几百万美元,并且更高的量产速度可显著影响收益。

在评测改进效果时,眼光狭隘失之片面。例如,如果过孔是可靠性和可制造性问题的根源,则不要只盯着那些 double-cut过孔,要逐个检查所有受保护和不受保护的过孔。受保护的过孔被定义为冗余过孔或者闭合严密的过孔。应将原始设计中所有受保护和不受保护的过孔与经过优化的设计中所有受保护和不受保护的过孔进行比较。

想当然地认为所有晶圆厂,甚至所有工艺节点都相同。事实上,每家晶圆厂和每个工艺节点都是不同的。例如,金属短路和开路的可能性随金属(如铝与铜)和工艺节点的不同而不同。应留出足够时间评估以前的DFx流程对新工艺产生的效果。

将晶圆厂建议的规则仅仅当作可选的规则。与晶圆厂一起共同确定一系列最影响良率的因素。应力图遵守这些规则,只有在无法满足设计(例如时序、功率)或区域目标时才能违反这些规则。加入一个检查/打分机制以评判在遵守被建议的规则方面你做得怎样。

对GDS数据进行所有的DFx增强工作。在这个阶段只能实现有限的一些几何方面的增强工作。可以采用可进行拓扑优化的工具在GDS之前进行DFx增强可得到最佳结果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)