(1)使用TTL集成电路注意事项

①TTL集成电路的电源电压不能高于+5.5V使用,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于+5.5V和低于-0.5V的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。如果将 图T306双列直插集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到VCC端。

④输出端不允许与电源或地短路。否则可能造成器件损坏。但可以通过电阻与地相连,提高输出电平。

⑤在电源接通时,不要移动或插入集成电路,因为电流的冲击可能会造成其永久性损坏。

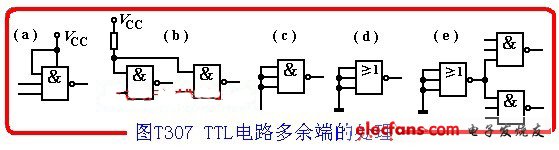

⑥多余的输入端最好不要悬空。虽然悬空相当于高电平,并不影响与非门的逻辑功能,但悬空容易受干扰,有时会造成电路的误动作,在时序电路中表现更为明显。因此,多余输入端一般不采用悬空办法,而是根据需要处理。例如:与门、与非门的多余输入端可直接接到VCC上;也可将不同的输入端通过一个公用电阻(几千欧)连到VCC上;或将多余的输入端和使用端并联。不用的或门和或非门等器件的所有输入端接地,也可将它们的输出端连到不使用的与门输入端上。如图T307所示。

对触发器来说,不使用的输入端不能悬空,应根据逻辑功能接人电平。输入端连线应尽量短,这样可以缩短时序电路中时钟信号沿传输线的延迟时间。一般不允许将触发器的输出直接驱动指示灯、电感负载、长线传输,需要时必须加缓冲门。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)