本文提出一种新的混沌RNG的实现方案,更易于用硬件即IC实现。首先讨论其原理和模型及其实验,并对其进行随机性测试;然后讨论它的FPGA实现方案。

1 模型及实验

1.1 随机数生成器的定义

定义1 一个理想的随机数生成器是一个生成等概率符号的离散无记忆信息源(DMIS),RNG是一个有着正熵的离散信息源。

但是,现实中的RNG都是产生非均匀概率符号的离散有记忆信息源。因此采用有偏差的RNG来区别于定义1中理想的RNG。一个有偏差的RNG性能的好坏可通过它的冗余度ρ=log2Q-h来衡量,其中Q和h分别是离散符号集的基数和相关信源的熵。一个理想RNG的冗余度应该等于O,而一个有偏差的RNG的冗余度则标志这个RNG跟理想RNG的差距。例如一个冗余度为ρ的RNG产生长度为N位的密钥,则攻击方平均要尝试2(1-ρ)N个密钥才能找到正确的密钥,因此密钥的有效长度可以被定义为Ne=(1-ρ)N。

1.2 混沌随机数生成器模型

混沌理论作为非线性动态系统的分支,近年来受到越来越多的关注。它使得一个低维动态系统也可以拥有复杂的、不可预料的行为,使复杂的方程不再是生成随机数序列的必要条件。

混沌系统可以用基于下列迭代关系式描述的Bemouli移位映射:

![]()

式中,e(n)表示一个高斯噪声信号。这个迭代式表明由(1)式产生的序列是极为平滑和均一分布的。另外,与混沌相关的轨迹发散包含了噪声,(1)式产生的序列在一定范围内是不可预测的,从而使系统能被当作一个真随机比特源。离散时间混沌法不受其他噪声源影响。

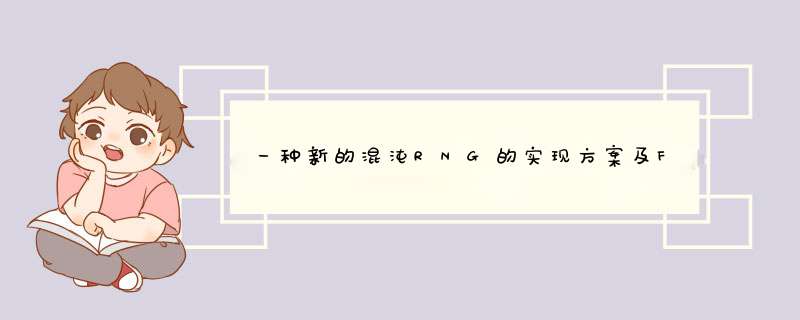

在电路上实现Bemouli移位映射的关键在于实现一个抗干扰的高斯噪声信号。传统的混沌随机数生成器是用一个伪随机数生成器产生一个伪高斯噪声信号来实现(1)中的e(n),如图1所示,这在一定程度上降低了混沌随机数生成器的安全性和真随机性。

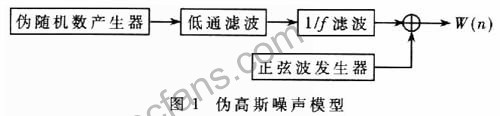

典型的振荡器采样法是利用时钟的相位噪声(理论上是MOSFET热噪声的副产品)产生随机数。通过一个由较慢时钟信号控制的D触发器对一个高速时钟进行采样,高速时钟的相位抖动导致具体采样值的不确定性,如图2所示,理论上每次采样都会产生一个随机比特。典型采样后的抖动电平是符合高斯分布的,而且这种抖动不会受到电路中其他噪声的干扰。另外,振荡器采样法的随机性可以通过仔细挑选快的和慢的时钟频率比来人为增强。采样时发生的非线性偏移现象使得这种振荡器采样技术比目前的确定性噪声更健壮。

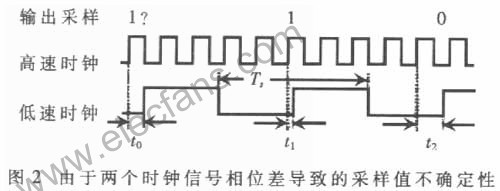

基于上述原理,提出用振荡器采样输出作为一个高斯噪声信号e(n)实现(1)式。结合两种随机数生成器方案实现混沌随机数生成器,系统原理框图如图3所示。

其中S/H(Shilt/Hold)为一个移位保持电路,用来实现2(x(n-1)+e(n))。低速时钟控制D触发器、寄存器和S/H。寄存器中残余信号作为初始输人信号,然后与振荡1.3 实验结果及讨论

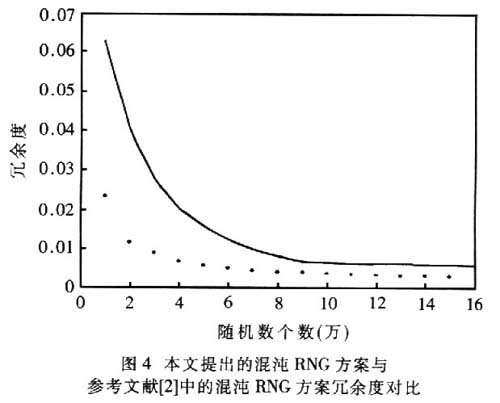

根据前面的定义l来检测本文中提出的混沌RNG的性能,用它生成不同长度的8bit随机数序列,计算其冗余度,并与参考文献中的传统混沌RNG方案做对比,如图4所示,点线表示本文提出的方案,实线表示69是文献中的方案。通过对比可以很明显地看出改进后的混沌RNC性能优于采用伪随机高斯噪声的传统混沌RNG方案。

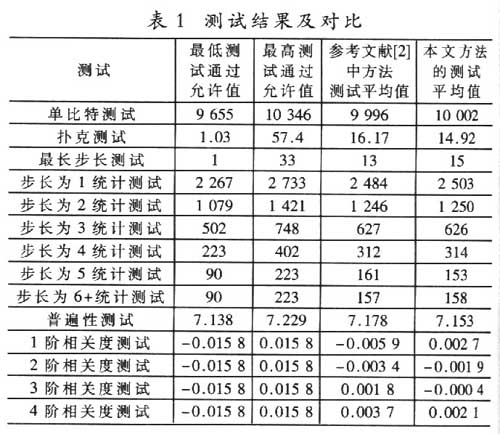

仅仅由冗余度来衡量一个RNG是不够的。为了了解本文提出的混沌RNG输出序列的随机性是否实现了“随机”,我们根据美国国家标准及技术研究所(NIST)的要求对本文的混沌RNC方案产生的随机数序列的随机性进行一系列测试。测试所用数据为慢速时钟=8kHz,高速时钟=100MHz,输出精度为8bit的输出值,测试长度为3 000 000个8位随机数的序列,表1为测试结果。

经过以上一系列的随机性测试,RNG表现良好,在置信水平为95%的情况下通过了全部测试,没有表现出非随机性,并且在信源相关度的测试(correlaTIon order test)中性能超过了参考文献中的混沌RNG方案。这项测试是测试一个随机数序列的相邻随机数的相关度。一个理想RNG的前后随机数相关度应该为0。由表1中数据可知,本文的混沌RNG测试结果更接近于理想RNG。因此可以认为,就目前已知的测试随机数的随机性的测试结果表明,本文介绍的混沌RNG生成的随机数序列是比较好的。

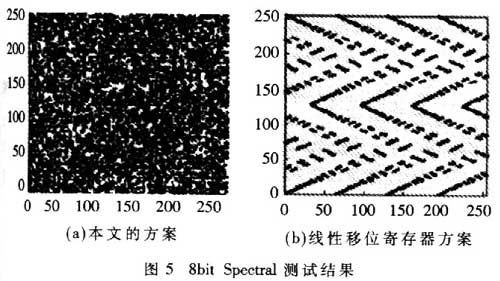

光谱测试可以直观地显示出随机数序列与其自身的相关情况。通过图5可以更直观地看到一个相关度低的RNG与一个伪RNG(用10位线性反馈移位寄存器来做例子)的对比。相关度为0的理想RNG应该均匀分布在整个二维空间内,线性反馈移位寄存器的测试结果(图b)就反映出了它的高相关度,而本文提出的混沌RNG方案的测试结果(图a)则显示了其不可预测性与无规则性分布。

2 硬件实现

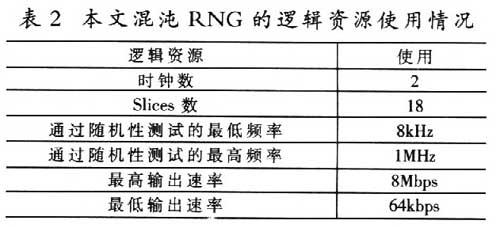

本文采用Xilinx公司的xuPV2P30开发板实现这个混沌KNG,这块开发板上自带两个独立的(不同相位)时钟源,二者都可以输出8k~100MHz的不同频率的时钟。选择慢速时钟信号频率范围为8k~1MHz,高速时钟信号频率为100MHz,输出精度为8bit。其逻辑使用资源情况如表2所示。

从表2可以看到,在硬件上以极低的逻辑资源使用(18个Slices约合1800+门)实现了本文提出的混沌RNG方案,对比参 考文献中的方案(3000+门),该电路得到大大简化,而参考文献中的伪高斯噪声生成器占用了很大的硬件资源。该方案的最高输出速率受到了板载最高时钟频率的限制。如果本文的混沌RNG用IC方案实现,则可以进一步减小所需要的硬件资源并进一步提高输出速率。

本文提出的方案通过了一系列高要求的随机性测试,其逻辑资源的占用远小于传统的混沌RNG方案,最高输出速率可达8Mbps。因而这种RNG方案可以用于对安全性和性能需求日益增长的加密系统中。

生成器采样输出信号进行模2加 *** 作(异或),再通过S/H产生最后的输出x(n),x(n)被反馈到寄存器中进行下次 *** 作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)