晶体振荡电路的设计方法

哈特莱振荡电路与考毕兹振荡电路等LC型振荡电路,其振荡率是由电路中的线圈与电容所决定的。此一线圈与电容器并非只是指电路图上所表示的组件数值,尚包含有晶体管的电极间容量印刷电路铜箔图样内所包含的L,C成分。

因此,由于温度、电源等变化所引起的L,C值变化,也会使振荡频率发生变化。

而晶体振荡电路为利用压电元件的固有振动数,因此,较不易受电路中的杂散L,C成分的影响,可以得到频率稳定度很好的振荡电路。

晶体/压电元件

为了提高振荡频率的稳定度,可以使用晶体或陶瓷(Cer-amic)振荡子等压电元件。此除了可以应用于高频率振荡电路以外,尚可以使用于钟表与计数器等基准时间产生电路。

压电元件为利用机械振动与电气振动间的相互转换的作用,而且其固有振动数是由几何尺寸所决定的。

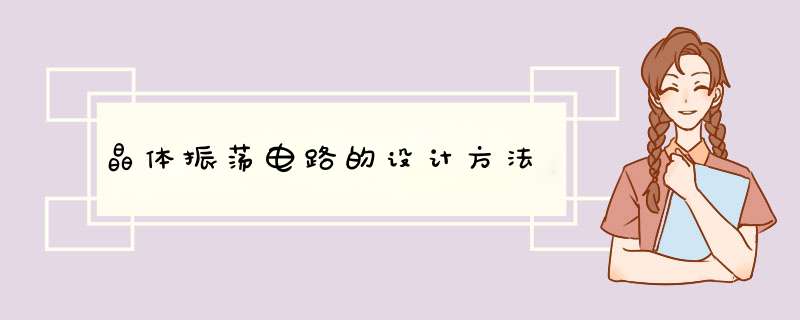

图25所示的为晶体的电气特性。

(由于使用振荡器,可以使频率更为稳定。振荡领域为在串联谐振点fs与并联谐振点fp之间。)

图(a)所示的为其等效电路,图(b)所示的为其电抗(Reaetance)特性。fs为串联谐振频率点fp为并联谐振频率点,其谐振频率分别如下:

,

将晶体与陶瓷振荡器此较,陶瓷振荡器的电感性范围fs~fp为晶体的数十倍。因此,陶瓷振荡器的频率稳定度比晶体差一些。

使用皮尔斯振荡电路

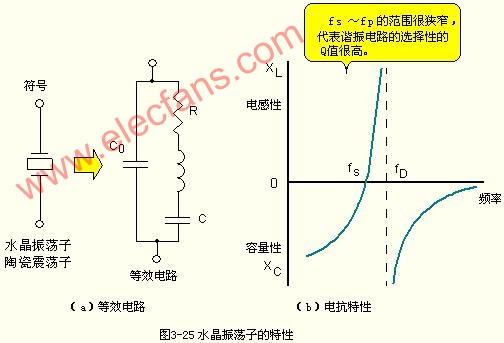

利用晶体振荡电路所构成的振荡电路称为皮尔斯振荡电路。

此一皮尔斯振荡电路为利用晶体的电感性电抗。将此一电感性(L性)部分当做线圈,可以应用在哈特莱电路或考毕兹电路。

图26的电路称为皮尔斯B-E电路。其原型为图(b)的哈特莱振荡电路。哈特莱振荡电路的电容器为利用晶体管的集极-基极间电容量Cab。

此一谐振电路的工作原理为振荡频率与f谐振频率fo成为fo>f 关系时,此一谐振电路呈现电感性(L),相当裁于线圈。

图(c)所示的为振荡电路的特性,将T的L先调整至最小,使谐振电路呈电感性。然后,再调整铁芯,使L增大,在谐振电路成为电容性时,会马上使振荡停止。接着,将调整点调至振荡停止点的稍微前方处即可。

图27所示的为皮尔斯C-B振荡电路,其原型为如图(b)所示的考毕兹振荡电路。

谐振频率fo与振荡频率f成为fo

无须调整的晶体振荡电路

在一般的皮尔斯电路中,需要调整谐振电路,此一电路并没有使用谐振电路,不必调整,也会产生振荡。

图28所示的为无调整晶体振荡电路。其原型为考毕兹振荡电路。

缺点是因为没有使用谐振电路,使得输出波形如照片4所示,成为含有很多高谐波成分的失真波形。

(虽然不必调整,但是,波形的高谐波成分多。可以用于数字电路的CLOCK时钟信号源。)

照片4:无调整晶体振荡电路的振荡输出波形

此一电路虽然为无调整,但是,仍然使用修整用电容(Tri-mmer)与晶体串联,使振荡频率可以微调整。

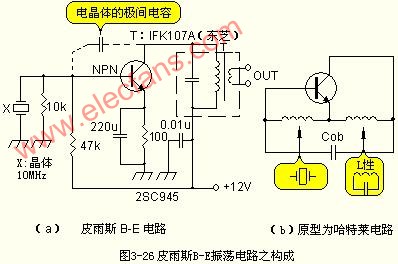

图29所示的为利用高谐波成分,取出基本波的3次高谐波,称之为3倍的overtone振荡电路。输出级的变压器为做为取出第3次高谐波用的滤波器。照片5所示的为其3次高谐波的波形。

(此为利用无调整电路的高谐波成分,在输出的谐振电路取出3倍频的30MHz信号。)

照片5 3倍频的振荡波形

(在无调整振荡电路的输出虽然包含很多高谐波成分。但是,利用频率选择电路可以得到良好的波形输出。)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)