当前集成电路制造技术迅速发展,SoC(system-on-chip)设计已经成为集成电路设计的发展方向。随着SoC 设计的复杂度提高,在开发SoC 的过程中,验证工作越发重要和繁重,所占的开销占据总开销的40%“70%。SoC 设计的验证过程不但影响到芯片的成功设计,而且影响到芯片的上市时间,因此验证的正确性及其耗时的缩短成为了SoC 设计的关键。

传统设计中,系统级设计使用高级语言C++/C++等描述功能模块的算法,验证的时候使用硬件描述语言(VHDL 或Verilog HDL)。系统验证之前必须通过手工将原始的C/C++代码转换为VHDL/Verilog HDL 代码,这个转换过程耗时大并且容易产生错误。在系统验证过程中,使用传统硬件描述语言对复杂模块的验证需要耗费大量时间。

为了提高系统级验证效率,本文针对视频芯片中的运动估计与补偿单元模块(MECU)提出了基于SystemC 的验证方法和流程。该方法大大缩短了系统验证的搭建时间和系统验证过程的时间。本文利用SystemC 支持设计者在不同抽象级建模的特点,给MECU 添加了低抽象级接口,使该单元能够和视频芯片内部其它模型通讯以便完成整个芯片的系统级验证。本文最后的仿真结果证明了该设计流程的有效性。

2 SystemC 语言SystemC 是由C++衍生而来,本质是在C++的基础上添加了硬件扩展库和仿真核,这使SystemC 可以在不同抽象级对复杂电子系统建模。它既可以描述纯功能的模型和系统体系结构,又可以描述软硬件的具体实现,进行软硬件的协同验证。

SystemC 包括以下建模元素:*模块(module) 相当于C++的类定义,是一个可以多层次的实体。一个模块可以嵌套其他模块和一些进程,是SystemC 里面最基本的单元。

*进程(process) 用来描述模块的功能,包含于模块中。进程是由事件(event)来触发的,这种触发的方式使进程可以并行执行,实现了硬件系统的并行特性,SystemC 包括三种不同的进程。

*接口(interface) 定义了一组方法实现目标,但是不实现这些方法。

*通道(channel) 实现了接口定义的方法,分为基本通道和层次化通道。

*端口(port) 总是与一定的接口类型相关联,端口只能连接到实现了该类接口的通道上,通过端口模块和进程来访问通道内定义的接口方法。

*信号(signal) 用来实现各个进程之间的通讯。SystemC 提供了多种信号格式来满足从寄存器传输级(Register Transmit Level, RTL)到功能级等不同抽象级的模拟。

*事件(event) 用来触发各个进程的开始以及暂停,通常多个事件组成一个敏感列表(sensiTIve list)共同决定进程的状态。

*时钟信号(clock) 时钟在同步电路设计中是一个非常重要的角色,本质上它是一种特殊的信号,为仿真过程提供了时间基准。

上述建模元素使得SystemC 能够顺利的搭建硬件平台。

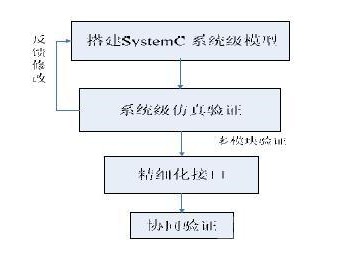

3 基于SystemC 的建模方法系统级验证过程中,对于复杂算法模型只需要建立参考模型(Reference Models),搭建验证平台,观察模型的一些重要功能(算法、进程等等),不需要了解RTL 层面的细节。利用事务级建模方法(TLM, TransacTIon Level Modeling)技术很容易建立参考模型。一个完整的芯片是由多个功能模块组成,采用SystemC 对复杂算法单元建立模型能使功能验证时间缩短,而一些简单模型的验证需要在RTL 层面。为了实现不同抽象级模块通讯,本文对使用SystemC 建立的复杂单元模型进行接口精细化处理。本文对实际芯片单元提出的SystemC 建模验证流程。

(1)搭建SystemC 系统级模型:

使用基于C++的SystemC 能很容易搭建系统级模型。利用SystemC 对所要实现的系统功能进行描述,主要描述系统的算法、结构等,不考虑每个时钟周期寄存器数值改变。只有针对复杂算法单元使用SystemC 建模,才能够发挥SystemC 节省建模和验证时间的优势。

(2)系统级功能仿真:

利用支持SystemC 的工具对建立的模型进行仿真验证系统功能,观察结果并且不断进行反馈修改直到仿真正确。

(3)精细化接口:

精细化接口是多模块验证过程的关键。因为在对单个复杂单元系统级验证的时候,抽象级很高,只需要考虑其功能性。多个模块验证时外部单元模型可能在RTL 级别构建,这时需要利用SystemC 能在不同抽象级建模的优势,在一个较大的模块中实现不同的抽象层建模,即在和外部模型接口处将抽象级降低到RTL 级。精细化接口的过程需要根据外部模块接口调节输入输出数据位宽、设置敏感事件列表,并且严格按照外部时钟控制数据的传输,保证顺利和外部模块通讯。

(4)协同验证:

验证多个模块共同工作的正确性,这时候发现错误就能够及时进行设计的修改,提高芯片设计效率。验证结果正确的模块就可以进行后端流程,建立的验证平台也可以作为外部驱动的测试平台进行软件的验证。

4 应用实例4.1 MECU 原理

广泛应用在手机中的视频编解码芯片编解码流程包括了DCT 变换、量化、VLC 编码、反DCT 变换,反量化、运动估计、运动补偿、插值计算、边缘填充等步骤,其中运动估计与补偿部分是实现压缩图像时间冗余度的重要环节,由于其算法的复杂性该部分占据了大部分的编解码时间, 对MECU 模块的验证是整个芯片验证中工作量最大的环节。

本文中MECU采用MVFast(MoTIon Vector Field AdapTIve Fast Motion Estimation) 算法实现ME/MC:ME 部分在图像编码过程中实现运动预测,计算出运动矢量,同时完成宏块编码类型(MBmode)判断和运动矢量编码类型判断;MC 部分在图像编码过程中,根据输入各块的运动矢量完成YUV 的插值处理输出运动参考块数据和当前处理块数据;在图像解码处理中完成插值处理输出参考块数据。

4.2 模块搭建

采用Verilog 语言直接建立MECU 模型用于芯片设计时,由于MECU 算法复杂,建模过程耗时巨大。Verilog 建模期间系统验证工程师需要等待模型建立完成,这样增长了芯片设计周期,另一方面对使用Verilog 建立的MECU 模型验证耗费时间长。由于基于SystemC的建模时间相对Verilog 建模时间缩短3~4 倍,验证过程具有快速性优势,本文尝试采用SystemC 进行前期建模和验证工作。

依据本文第二部分介绍的验证方法,首先建立MECU 硬件仿真模型进行功能验证,然后在这个硬件模型正确的基础上进行外围模块设计的验证,以实现整个芯片的系统级验证。

第一步利用SystemC 对ME 和MC 分别进行系统级建模。在建立ME 和MC 这两个模块时,只需要实现ME 和MC 各自算法功能和两个模块之间的通讯,因此不需要按照精确的时序建模。在C 语言实现MVFAST 算法模型基础上,用SC_MODULE 将ME 和MC 各自编写成可仿真的模块MEU 和MCU,内部的功能利用Process 来实现。模型建立之后,搭建平台进行功能验证,观察数据经过ME 和MC 之后的变化是否完全符合算法要求。

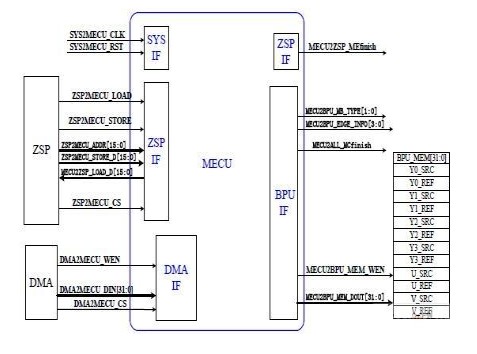

MEU 和MCU 模型功能验证结束之后需要协同芯片中其它模块进行验证,由于MECU的外围模块是在RTL 级建模,并且严格按照时钟进行数据处理,因此必须对MECU 接口进行精细化。本实验添加了SYS_IF ,ZSP-IF, DMA-IF 和BPU-IF 模块以实现与外围模块通讯,这些接口模块包括和外围模块相匹配的输入输出端口,并且由时钟严格控制数据的传输。

4.3 接口模块描述

(1)SYS_IF 提供MECU 的外部时钟以及复位信号接口,这两个控制信号对MECU 内部所有模块有效。

(2)MEU 和MCU 的触发由外部ZSP 产生的开始信号来控制,在MECU 内部包含的控制寄存器也由ZSP 来控制。ZSP_IF 模块的添加实现了ZSP 对MECU 进行读写控制。

(3)MECU 模型编解码过程需要处理的数据是通过ZSP 控制DMA 提供,因此添加DMA_IF模块实现和DMA 通讯,搬运数据以供MECU 处理。

(4)最终MC 完成产生的数据,通过BPU_IF 模块传输出到BPU 中(用于软硬件结果对比)。

从上述结构可以看出,MECU 包括了六个模块:ME,MC,SYS_IF,ZSP_IF, DMA_IF 以及BPU_IF。ME 和MC 作为核心功能模块实现了MECU 单元的算法,SYS_IF,ZSP_IF, DMA_IF以及BPU_IF 四个接口模块由时钟严格控制数据的传输,实现和外围模块通讯功能。

5 仿真结果分析

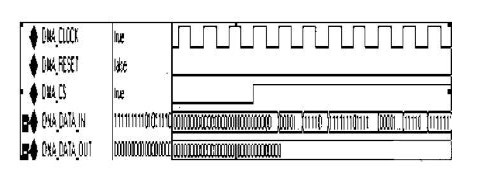

利用上述SystemC 模型进行仿真验证,采用一组352*288 像素的图像作为仿真对象,使用Mentor 公司的Modelsim 作为仿真工具。首先建立测试平台,对外部ZSP,DMA 进行模拟以提供控制信号和处理数据,然后利用Modelsim 进行仿真验证和时序分析。

仿真得到的数据结果完全符合算法的期望值,证明了搭建模型的正确性。时序分析结果表明:使用SystemC 对图像的一个宏块(16*16 像素)进行编码平均需要680 个clock cycle,其中ME 和MC 部分占用11 个clock cycle;用传统硬件描述语言Verilog 建模进行验证一个模块的编码平均需要3000 个clock cycle,其中ME 和MC 占据2200 个clock cycle。将基于SystemC 和Verilog 两种建模方法的ME 和MC 验证时间相比较发现:采用SystemC 进行纯功能性验证时间比使用Verilog 验证时间缩短了约200 倍,因此验证时间上的优势是显著的。

6 总结本文对 SystemC 验证方法进行了深入的研究,针对视频编解码芯片MECU 单元的验证提出了使用SystemC 验证的建模流程,通过端口细化方法使芯片能在不同抽象级建模验证,这种方法在当前国内验证方面使用不多。仿真结果证明了该流程的有效性,和使用传统硬件描述语言验证相比时间显著缩短。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)