1 LED显示屏控制系统对串行FRAM的要求

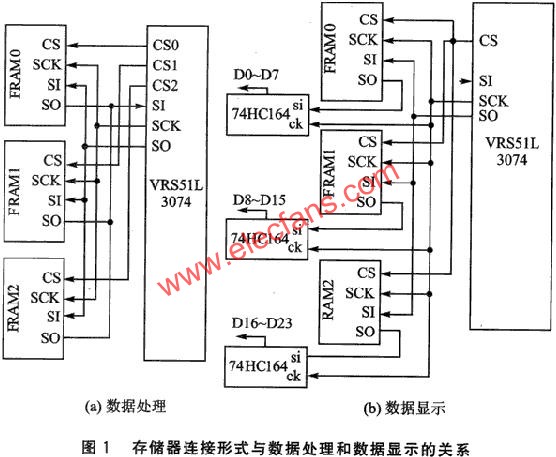

首先,对VRS51L3074控制的3个FRAM组成的数据处理系统与FRAM的连接关系进行分析。图1(a)为VRS51L3074和3个FRAM组成的数据处理系统。当进行显示数据处理时SPI总线为标准连接形式,即所有SPI接口芯片的SI、SO、SCK分别连接在一起;只有片选线分别与 VRS51L3074连接,对每一个存储器的数据分别进行读写 *** 作。而数据显示时只需同步给定3个串行存储器相同的起始地址,然后在SCK脉冲的作用下由串行FRAM存储器的SO脚送入74HCl64,经串并转换后直接输出到LED显示屏。由于显示数据直接由74HCl64旁路“DMA”至LED显示屏,因此作为数据显示控制的VRS51L3074不需要处理串行存储器的输出数据,也就是说对3个串行存储器只需要进行开环控制。具体电路框图如图1(b)所示。

2 双端口RAM模块及LED显示屏控制系统

图2所示的串行双端口RAM模块是根据图1中数据处理和数据显示SPI的连接关系,外加总线开关74HC245构成的。SPI接口的FRAM时钟信号 SCK和数据输入端SI共用,而由于驱动LED显示屏时3个片选信号要同时有效,数据输出SO端(如图1(b)所示,分别接3片74HCl64的输入端) 也需要独立控制,故需要由74HC245总线开关实现在端口A、B间切换的控制信号为8个(SI,1个;SCK,1个;CS,3个;SO,3个),使用2 片8总线数据开关74HC245就足够了。

图3为由2个串行双端口RAM模块构成的LED显示屏控制系统。工作时数据处理单片机与数据显示单片机通过2条控制线进行同步工作,其中数据处理单片机为主机,数据显示单片机为从机。在实际应用中,可通过增加串行双端口RAM模块的数量,或增加74HCl64的级数来增加LED显示屏的高度。LED显示屏水平方向的长度只与数据显示单片机以及串行FRAM的SPI时钟频率有关,在SPI时钟频率为20 MHz时,水平方向的长度可达2 048点。在双向驱动模式下,LED显示屏的高度由串行双端口RAM模块的数量确定。水平方向的长度在40 MHz时无灰度可达4 096点,在8级灰度情况下可达512点;而垂直方向3片FRAM经74HCl64串并转换后的3字节(共24位),双色点数=24÷2x16=192 点,单色点数=24×16=384点。

FM25L256B串行FRAM的读写与串行Flash基本一致。最大的特点是写一个字节后不需要像串行Flash那样查询写 *** 作是否完成,而是像顺序读 *** 作一样连续写;既不需要先擦除再写入,也没有读写次数的限制,完全可像RAM一样使用。VRS51L3074的SPI接口速度为系统时钟的1/2,一般 51单片机的SPI接口速度都是系统时钟的1/4(没有下载脉冲),因此VRS51L3074的SPI接口的某些特性在LED显示屏控制系统中有极为重要的作用。同样,串行FRAM和VRS51L3074共同构成的双端口RAM控制系统,可利用VRS51L3074的SPI接口非常方便地完成多字节读写。

3 双MCU共用双端口RAM协同工作

首先,数据处理单片机在模块O和模块1中组织同样的显示数据,然后通过显示控制端启动数据显示单片机。数据显示单片机对串行FRAM只有读的权力,只能同时通过CSO片选模块0或1中的3片FRAM,并通过SO端同时给模块O或l中的3片FRAM送显示数据的首地址;然后在SCK的作用下,模块 O或1中的3片FRAM通过各自的SO端向对应74HCl64的SI端输出显示数据,同时由数据显示单片机通过CS3端自动产生LED显示屏单元板所需的移位脉冲。在LED显示屏一行显示完成后,数据显示单片机向数据处理单片机发出行显示完成的状态信号,同时等待数据显示单片机发出继续显示的指令,当接收到继续显示指令后启动下一行的显示。数据处理单片机可根据需要通过端口选择让数据显示单片机显示模块O或1中的显示数据,且单片机可在数据显示单片机显示的同时,处理双端口RAM模块1或O中的显示数据。

结语

本文对LED显示屏控制系统使用由串行FRAM存储器组成双端口RAM的硬件系统和控制方法进行了初步的探讨。这种双端口RAM与传统双端口RAM的不同之处在于其端口的一端可读写,而另一端只能读。利用串行FRAM组成双端口RAM具有控制线少、容量大及价格低等优点,在读写速度要求不是很高的情况下有着良好的应用前景。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)