子系统划分选择方案

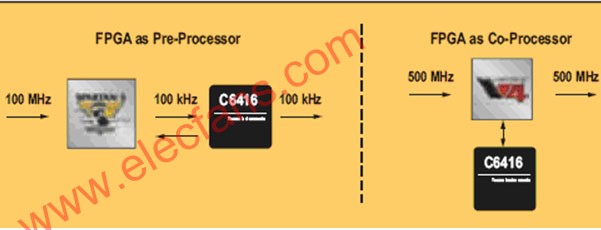

FPGA可与DSP处理器一起使用,作为独立的预处理器(有时是后处理器)器件,或者作为协处理器。在预处理架构中,FPGA直接位于数据通路中负责信号预处理,预处理后的信号可以高效又经济地移交给DSP处理器进行速率较低的后续处理。

在协处理架构中,FPGA与DSP并列而置,后者将特定算法函数卸载给FPGA,以便实现比单独采用DSP处理器能达到的速度更高的处理速度。FPGA的处理结果传回DSP,或者送至其他器件进一步进行处理、传输或存储(图1)。

选择预处理、后处理还是协处理,常常取决于在处理器和FPGA之间移动数据所需的时序余量及其对整体延迟的影响。虽然协处理解决方案是设计人员最常考虑的拓扑结构(主要是因为DSP可以更直接地控制数据移交过程),但这并不一定总是最佳的总体策略。

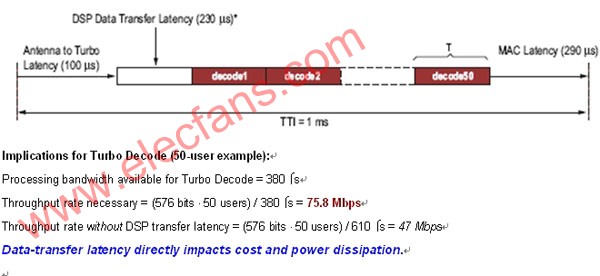

例如,最新的3G LTE规范将传输时间间隔(TTI)从HSDPA的2ms和WCDMA的10ms缩短到了1ms。这实质上是要求从接收器一直到MAC层输出之间的数据处理时间短于1,000?sec。

图1:FPGA 用作预处理器和协处理器的解决方案

如图2所示,在运行速度为3.125Gbps的DSP上使用SRIO端口(使用8b/10b编码,Turbo解码功能需要200比特的额外开销)会造成230?sec的DSP到FPGA传输延迟(也就是说TTI时段中有将近四分之一仅用来传输数据)。加之其他可预见的延迟,为满足这些系统时序,当用户为50个时,所需的Turbo编解码器性能就是高达75.8Mbps。

图2:协处理数据传输延迟问题的 LTE 示例

使用FPGA将Turbo编解码器作为基本上独立的后处理器来处理,不仅可消除DSP延迟,还能节省时间,因为不需要以高带宽在DSP和FPGA之间传输数据。这样做可将Turbo解码器的吞吐量降至47Mbps,因而可选用更多比较经济的器件,并且可以减少系统功耗。

另一项考虑是在XilinxFPGA上是否使用软嵌入式或硬嵌入式处理器IP来卸载某些系统处理任务,进而可能进一步减少成本、功耗和占用空间。有了如此大量的信号处理资源,就可以在DSP处理器、FPGA可配置逻辑块(CLB)、嵌入式FPGA DSP模块和FPGA嵌入式处理器之间更好地分配各种复杂功能(如基带处理中的复杂功能)。Xilinx提供了两种类型的嵌入式处理器:MicroBlaze软核处理器(常用于系统控制)和性能更高的PowerPC硬核嵌入式处理器(用于更复杂的任务)。

FPGA嵌入式处理器提供的有利条件允许将所有非关键性 *** 作都合并到在嵌入式处理器上运行的软件中,从而尽量减少整体系统所需的硬件资源总量。

软件和IP的重要性

关键问题是如何将这种潜在能力全部释放出来。必须考虑需要用哪些软件对问题的复杂性进行抽象以及可以使用哪些IP,应该考虑利用FPGA为关键部分提供最佳解决方案。

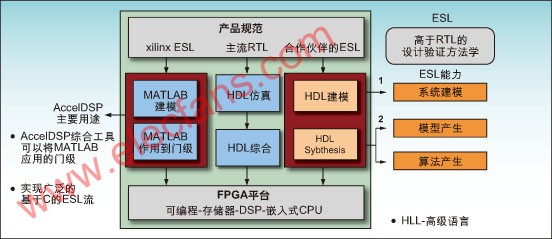

Xilinx致力于开发行业领先的工具和体系,能够在比HDL工具(如MATLAB模型和C代码)所能提供的更高的抽象层上实现高效的FPGA解决方案。利用Xilinx专门用于DSP的系统生成开发工具和AccelDSP综合工具,可以尽可能无缝实现从算法到硅片的链接。

目前有一个日益重要的工具提供商团队,其产品通过C++/C++到逻辑门的设计流程把开发提升到电子系统级(ESL)。ESL设计工具的目的是提供一种完备的系统级方法,以便生成和集成硬件加速功能以及控制这些功能的处理器的控制代码。

没有哪一种高级语言或软件工具能适合当今复杂系统中所见的所有不同单元。语言和设计流程的选择取决于客户,有时取决于具体的工程师。因此,Xilinx开发了一套齐全的集成功能,以满足客户需求并提供最佳设计环境(见图3)。

图3:系统级到 FPGA 设计流程

本文小结

另外,Xilinx正在斥巨资提供一套功能广泛的高价值IP、电路板和参考设计,以涵盖射频卡和基带应用中的许多关键部分,其中包括FFT/iFFT、调制、数字上下变频和波峰系数的降低电路等。

这一重点举措的一个例子是开发针对特定无线标准和FPGA架构优化的行业领先的高性能FEC功能,如Turbo编码器和解码器。正如我们在分析3GLTE延迟和Turbo解码器流量要求时所示,FEC功能的硬件加速及其对系统架构的作用在现代无线设备设计中是日渐紧要的当务之需。

虽然一些专家级DSP处理器陆续以嵌入式模块的形式集成这类功能,但是,从制订出符合新无线标准的FEC功能参数到形成嵌入式加速模块出现在硅片中,通常需要好几个月。一旦实现了嵌入,也还会有遗留的难题,偶尔还会有嵌入式模块中的功能并非都能按要求工作的局面出现。同时,标准演化迅速,现标准中不时纳入一些固定嵌入式模块不能支持的新要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)