QPSK是数字通信系统中一种常用的多进制调制方式。其调制的基本原理:对输入的二进制序列按每两位码元分为一组,用载波的四种相位表征它们。实际上QPSK信号是两路正交双边带信号。现在人们对通信的要求越来越高,高速率、大容量、以及多业务,这些对有限的频谱资源构成了大的挑战。因此,对相移键控的研究具有重要意义,因为信道条件的限制,大多数数字通信系统采用了对幅度波动不敏感的频移键控、相移键控和相应的派生调制方式。

基于以上QPSK调制,本设计基于CPLD采用相位选择法来实现调制。

1。 QPSK调制原理

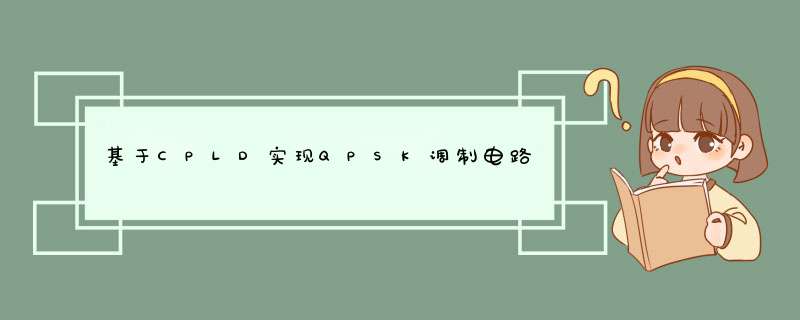

QPSK信号的正弦载波有4个可能的离散相位状态,每个载波相位携带2个二进制符号(00、01、10、11),其信号表示式为图1(a)是载波初始相位为0°的QPSK信号矢量图,如上图1(b)是初始相位为45°的QPSK信号的矢量图。

图1QPSK调制有两种产生方法:相乘电路法和相位选择法。

乘法电路调制:二进制码经过串并变换器分为两个半速率双极性码,两路信号经过低通滤波,分别与相互正交的两路载波信号相乘,然后两路信号相加得到QPSK信号。

相位选择法:输入二进制数据经过串/并变换输出双比特码元,四相载波产生器输出四种不同相位的载波,逻辑选相电路根据串/并变换输入的双比特码元,每个时间间隔选择其中一种相位的载波作为输出,然后经带通滤波器滤除带外干扰信号,就得到QPSK调制信号。

2. 本设计调制原理

在设计中采用相位选择法来实现,QPSK信号有四种状态(00、01、10、11),将输入二进制序列每两位码元分为一组。

方案中,用四种波形表示四种相位(图2)

图2 用四种波形表示四种相位

3. 系统模块设计

电路总分为6部分:

第一部分:电源电路,为整个电路提供5V的电压;

第二部分:时钟信号电路,用来产生一个4MHz的时钟;

第三部分:基带信号产生电路,产生五种序列码(全0码、全1码、0\1码、7位M序列和15位M序列);

第四部分:调制电路,实现基带信号调制成抽样信号输出;

第五部分:D/A转换电路,将调制模块输出的信号转换成模拟信号输出;

第六部分:滤波电路,对D/A转换后的模拟信号经滤波完成模拟信号重建。

3.1 电源模块

为电路提供5V电压的设计实现方案有多种,如采用USB提供5V电压也可以设计直流稳压电源。直流稳压电源的设计要先采用电源变压器经过整流电路然后滤波最后稳压这四部,设计实现起来相对复杂。设计中购买9V输出电源,将9V电源转化为5V电源。电路由一个7805芯片和2个电容组成,7805的1脚接电源电压输入,2脚接地,3脚经稳压后输出5V电压。C1、C2用来滤出纹波。

3.2 时钟信号模块

时钟电路模块由2个反相器构成反馈,配合1个电容和2个电阻使晶振起振,来产生一个4MHz的时钟。

3.3 基带信号产生模块

此模块的作用是产生五种基带信号(全0码、全1码、0\1码、7位M序列和15位M序列)。

3.4 D/A模块

调制模块调制出来的信号是数字基带信号,需要经过D/A转换为模拟信号,在设计中选用DAC0832实现D/A转换。

DAC0832输出的是电流,但要求输出是电压,所以电路还必须经过一个运算放大器转换成电压。

3.5 滤波模块

滤波电路在设计中采用的是一个压控电压源低通滤波器。其截至频率为50KHz,增益为2,K=5.

4. 调制信号仿真

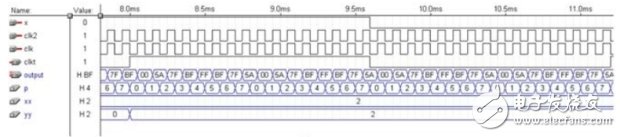

调制信号的仿真结果如下:

当输入0/1码时,由于寄存器y为2,所以循环输出电平为005A7FBF.FFBF7F5A仿真波形如图3所示。

图3

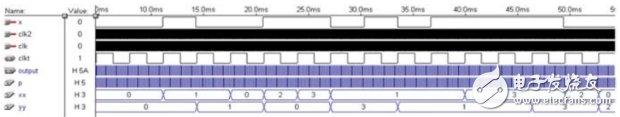

当输入15位M序列码时,由于寄存器y值是变化的,所以输出电平不是循环的,仿真波形如图4所示。

图4

5. 结束语

本次设计主要硬件模块有基带信号产生模块、调制模块、D/A转换模块和滤波模块,其中为简化设计系统设计供电模块采用了5V电池供电,基带信号产生模块和调制模块是设计中的关键点和难点,其基于CPLD设计,CPLD是一种整合性较高的逻辑逻辑元件。有高整合性的特点,故其有性能提升,可靠度增加,PCB面积减少和成本低等优点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)