本文介绍了IGLOO系列主要特性和优势,IGLOO系列架构框图以及采用AGL125的马达控制子板主要特性,步进马达控制逻辑方框图,BLDC马达控制逻辑方框图以及马达控制子板电路图和材料清单。

IGLOO系列主要特性和优势:

Low Power

• 1.2 V to 1.5 V Core Voltage Support for Low Power

• Supports Single-Voltage System OperaTIon

• 5 μW Power ConsumpTIon in Flash*Freeze Mode

• Low Power AcTIve FPGA OperaTIon

• Flash*Freeze Technology Enables Ultra-Low Power Consumption while Maintaining FPGA Content

• Easy Entry to / Exit from Ultra-Low Power Flash*Freeze Mode

High Capacity

• 15 k to 1 Million System Gates

• Up to 144 kbits of True Dual-Port SRAM

• Up to 300 User I/Os

Reprogrammable Flash Technology

• 130-nm, 7-Layer Metal, Flash-Based CMOS Process

• Live-at-Power-Up (LAPU) Level 0 Support

• Single-Chip Solution

• Retains Programmed Design When Powered Off

• 250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance

In-System Programming (ISP) and Security

• Secure ISP Using On-Chip 128-Bit Advanced Encryption Standard (AES) Decryption (except ARM®-enabled IGLOO® devices) via JTAG (IEEE 1532–compliant)†

• FlashLock® to Secure FPGA Contents

High-Performance Routing Hierarchy

• Segmented, Hierarchical Routing and Clock Structure

Advanced I/O

• 700 Mbps DDR, LVDS-Capable I/Os (AGL250 and above)

• 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

• Bank-Selectable I/O Voltages—up to 4 Banks per Chip

• Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V / 2.5 V / 1.8 V / 1.5 V / 1.2 V, 3.3 V PCI / 3.3 V PCI-X,and LVCMOS 2.5 V / 5.0 V Input†

• Differential I/O Standards: LVPECL, LVDS, B-LVDS, and MLVDS (AGL250 and above)

• Wide Range Power Supply Voltage Support per JESD8-B, Allowing I/Os to Operate from 2.7 V to 3.6 V

• Wide Range Power Supply Voltage Support per JESD8-12, Allowing I/Os to Operate from 1.14 V to 1.575 V

• I/O Registers on Input, Output, and Enable Paths

• Hot-Swappable and Cold-Sparing I/Os‡

• Programmable Output Slew Rate† and Drive Strength

• Weak Pull-Up/-Down

• IEEE 1149.1 (JTAG) Boundary Scan Test

• Pin-Compatible Packages across the IGLOO Family

Clock Conditioning Circuit (CCC) and PLL†

• Six CCC Blocks, One with an Integrated PLL

• Configurable Phase Shift, Multiply/Divide, Delay Capabilities, and External Feedback

• Wide Input Frequency Range (1.5 MHz up to 250 MHz)

Embedded Memory

• 1 kbit of FlashROM User Nonvolatile Memory

• SRAMs and FIFOs with Variable-Aspect-Ratio 4,608-Bit† RAM Blocks (×1, ×2, ×4, ×9, and ×18 organizations)

• True Dual-Port SRAM (except ×18)†

ARM Processor Support in IGLOO FPGAs

• M1 IGLOO Devices—Cortex™-M1 Soft Processor Available with or without Debug

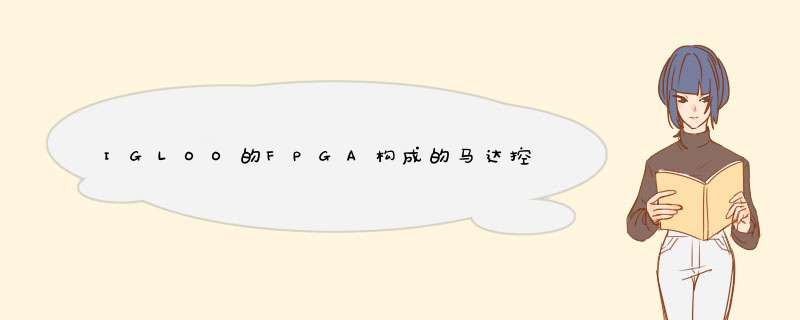

图1。IGLOO系列架构框图(AGL015, AGL030, AGL060和AGL125)

马达控制子板

The Motor Control daughtercard provides a design reference and evaluation kit for motor control using Actel’s ultra-low power IGLOO® FPGAs. This daughtercard, co-developed with Actel and Ishnatek, is available exclusively from Avnet Memec. The board is designed to work with Actel’s IGLOO Icicle™ Kit (ordered separately) and attaches to the Icicle kit’s accessory board edge connector.

马达控制子板主要特性:

• Supports

Stepper Motor (4-Wire Configuration)

Full Step / Half Step Mode

Micro Step Mode (Trapezoidal Option)

8 / 16 Microsteps

Brushless DC (BLDC) Motor (Three Phase BLDC Motor)

Sensored Drive

• Using Hall Effect Sensors provided on Motors

• Direction Control – Clockwise or Counterclockwise Rotation

• Basic Functions

Start

Stop

Step ( Full or Half Stepping in case of Stepper Motor)

RPM+/RPM- (Increase/Decrease RPM)

Digital Control Features

• Support Two PWM Modes

PWM on high side of Mosfet Bridge

PWM on low side of Mosfet Bridge (Available but not supported)

• Hardware/Software Control

Access to all above features through keys/switches on board

Equivalent controls are provided also through software

Software Interface using on-board USB-to-RS232 bridge on Icicle

• High Output Current up to 2 A

图2。马达控制子板外形图

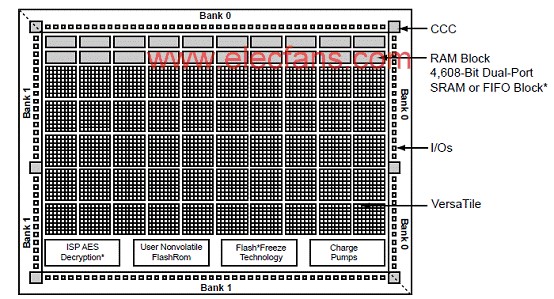

图3。步进马达控制逻辑方框图

图4。BLDC马达控制逻辑方框图

图5。马达控制子板电路图(1)

图6。马达控制子板电路图(2)

图7。马达控制子板电路图(3)

马达控制子板材料清单(BOM):

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)