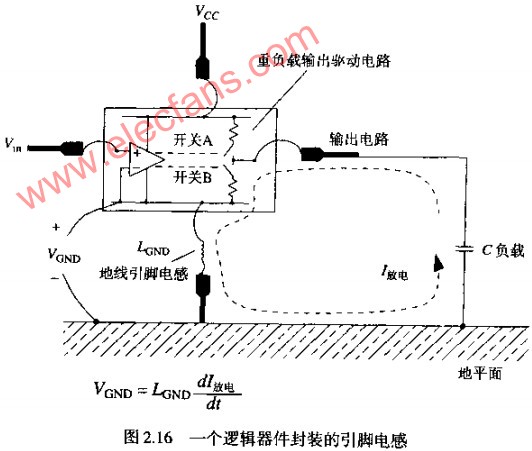

图2.16描绘了一个理想逻辑器件管芯引线连接的四引脚双列直插式封装器件。包含一个发送电路和一个电路。发送电路是推拉输出电路,而事实上任何构造的电路在高速情况下都同样会出现这一问题。

假定输出驱动器的开关B刚刚关闭,负载电容C对地放电。随着电容的下降,它积累的电荷向地,在接地回路上形成一个大的电流浪涌,图中标为:I放电。

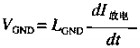

随着放电电流建立然后衰减,这一电流变化通过接地引脚的电感起作用,在器件外的系统地平面与封装内的地之间感应产生了一个电压VGND。这个电压的值等于:

由于输出转换而引起的内部参考地电位漂移称为“地d”

与满幅值的输出电压相比,地d电压VGND通常很小。它不会严重地削弱发送信号,但严重干扰了接收。

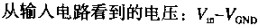

再来考虑同一管芯内的接收器电路部分。接收器把输入电压VM与它本地的内部参考地进行差分比较。这个差分运算在图2.16中可以看成连接到VIN的正输入减去连接内部地的负输入。因为内部的地携带了VGND噪声脉冲,从输入电路看到的实际电压差等于:

因为输入电路对它的正和负输入之间的差值做出了响应,它无法知道噪声脉冲VGND是被加到负输入,还是从正输入减去。换句话说,从输入电路看来,VGND脉冲就像是直接叠加在输入信号上的噪声。

如果同一芯片上到N个容性负载相应的N路输出同时转换,会得到N倍的地电流,于是脉冲VGND的增大也接近N倍。

地d电压与经过地线引脚的电流变化率成正比。当驱动容性负载的时候,我们期望变化率看起来像电压的二阶导数一样。参考图2.14,电压的二阶导数是一个双峰波形,首先向上隆起,然后向下凹陷。

本文地址:https://www.elecfans.com/arTIcle/analog/2010/20100602218826.html

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)