1 Adsp-TS101的主要性能

Adsp-TS101的主要性能如下:

采用TIgerSHARC结构,具有3条独立总线用于取指令、取数据、不间断I/O;

指令周期4 ns,工作时钟250 MHz;

单指令流多数据流(SIMD)提供两个运算单元,每个有一个算术逻辑单元、乘法器、移位器、寄存器组,可同时在两个运算单元上进行同一指令下对不同数据的32位 *** 作;

提供最大1 500 MFLOPS运算能力;

片内6 M位双口SRAM,允许CPU、Host和DMA的独立存取;

有14个DMA通道,可进行内存和外存、外设、主处理器、串(serial)口、链路(1ink)口之间的数据传输;

有2个数据地址发生器(IALU),允许取模和按位取反 *** 作;

片内集成I/0处理器、6 M位双口 SRAM,具有串行、连接、外部总线和JTAG测试口,支持多处理器结构;

并行总线和多运算单元,使单周期可执行1次算术逻辑运算、1次乘法、1次双口SRAM的读或写,以及1次取指 *** 作,CPU与内存之间可进行每周期4个32位浮点字的传输;

簇式多处理器最高可支持8个TIgerSHARC Adsp-TS101。

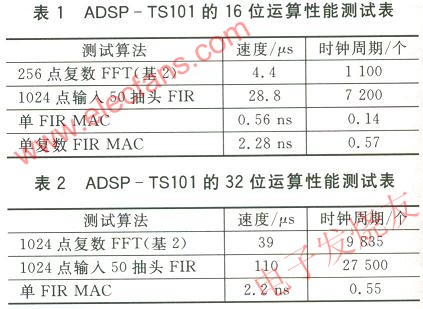

Adsp-TS101性能测试如表1、2所列。

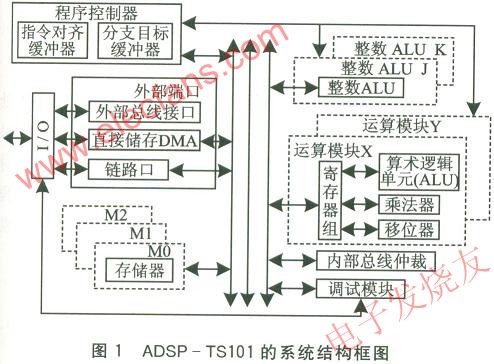

2 Adsp-TS101的系统结构框图和功能简介

图1为ADSP一TSl01的系统结构框图。由图可见,Adsp-TS101包括PEX、PEY两个运算单元,每一个浮点运算有一个算术逻辑单元、乘法器、移位器、32字寄存器组。另外,算术逻辑单元、乘法器、移位器为并行排列,可进行单周期多功能 *** 作,如在同一机器周期中算术逻辑单元和乘法器可同时进行 *** 作。

当数据在存储器和寄存器之间传递时,IALU提供存储器的地址。每个IALU有一个算术逻辑单元、32字寄存器组。

程序控制器包括指令队列缓冲器(IAB)和分支目标缓冲器(BTB)。Adsp-TS101既有4个外部中断IRQ3~O,也有内部中断。

3条128位总线提供高的宽带连接。每个总线允许每个周期4条指令或4队列数据进行传输。外部口和其他链路口的片上单元也用这些总线访问存储器。在每个周期仅能访问一个存储器块,故DMA或外部口传输与处理器核在访问同一块时必须进行竞争。

片内6 M位SRAM,分为3个(M0、M1、M2)128位宽的2 M位的块,可组合构成数据、程序存储器,每个SRAM与两个总线相连,允许单周期内完成和CPU之间4个数的传输。

外部口支持与片外存储器、主机(host)及8片Adsp-TS101的多处理器接口。外部口支持同步、异步及突发式存取。

Adsp-TS101提供了4个链路口,每个链路口是8位双向口,与SHARC DSP口不兼容。

DMA控制器支持独立于处理器的后台零等待数据传输。14个DMA通道分别与外部口(4)、链路(1ink)口(8),autoDMA寄存器(2)相连,外部总线可采用8/16/32/64位字长进行DMA *** 作。此外还有JTAG测试口及片内仿真。

串口支持250 Mb/s的收发独立的同步传输。

具有IEEE JTAG标准1149.1测试口和片内仿真。

27 mm×27 mm或19 mm×19 mm PBGA封装。

内部ADD1.2 V,外部ADD3.3 V。

3 Adsp-TS101的典型应用

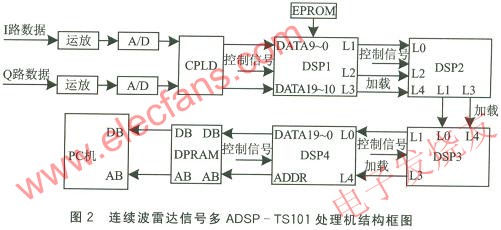

根据ADSP-TS101的系统结构特点,给出Adsp-TS101在雷达信号处理方面的典型应用,如图2所示。信号处理机主要由以下几部分组成。

① 运放及A/D。DPMCW接收机视频输出信号幅度为O~+4 V,经运放接收后,输出到A/D的模拟输入端。运放及A/D分为I、Q两路输入,以32位定点数同时采集到DSP1,在DSP1内分为I、Q两部分进行处理。

② CPLD。CPLD内部主要完成对数据的锁存,产生A/D采样时钟、各个DSP的中断请求信号和数据发送的同步信号。

③ DSP1。DSP1主要完成:A/D数据输入变换,并输出到DSP2;系统自举。系统采用EPROM自举方式,4个DSP的加载任务由DSP1完成。初始化时,DSP1通过链路口1发出一个控制字,将工作参数传给DSP2、DSP3、DSP4。链路口3和链路口4用于系统自举。

④ DSP2。DSP2完成2048点FFT运算。输入数据用链路口0和链路口2,输出数据用链路口1和链路口3。链路口4用于系统自举。

⑤ DSP3。DSP3完成门限判断与固定目标对消和动目标运动速度的校正。

⑥ DSP4和DPRAM。DSP4完成数据积累,然后对数据进行整理并输出。

这个例子充分体现了ADSP-TSl01适宜多处理器结构,通过链路(1ink)口支持串行处理器,而不需要任何附加逻辑电路的优势。

4 电源供电及功耗估计

(1) 电源供电

Adsp-TS101有三个电源,其中数字3.3 V为l/0供电;数字1.2 V为DSP内核供电;模拟1.2 V为内部锁相环和倍频电路供电。Adsp-TS101要求数字3.3 V和数字1.2 V同时上电。如果无法严格同步,则应保证核电源1.2 V先上电,l/0电源3.3 v后上电。本系统在数字3.3 V输入端并联了一个大电容,而在数字1.2 v输入端并联了一个小电容。其目的就是为了保证3.3 v充电时间大于1.2 v充电时间,以便很好地解决电源供电先后的问题。

(2)外部口功耗估计

外部口的功耗主要是输出引脚(例如数据线的某个位由高到低,或由低到高)转换的功率消耗,而且该功耗与系统无关。由于这种转换的外部平均电流为0.137 A,因此,功耗为PDD=VD×lDD=3.3 V×0.137 A="0".45 W

(3)内核功耗估计

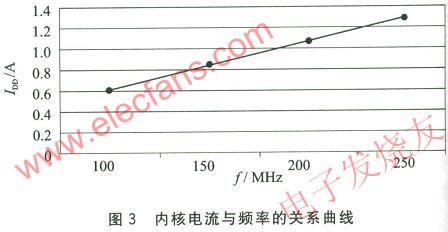

内核最大电流为1.277 A。该电流是DSP进行单指令流多数据流(SIMD)方式下,4个16位定点字乘加与2个四字读取并行 *** 作以及进行由外部口到内部存储器DMA *** 作所需的电流。实际上,DSP内核电流大小还和内核工作频率有关,图3所示是其内核电流与频率的关系曲线。因此,供给DSP内核电流可根据不同的并行处理任务和内核工作频率来确定。若并行处理较少,工作频率低,所需电流就小。这样,最大内核功耗为PDD=VDD×IDD=1.2 V×1.277 A="1".534 W。

结 语

本文介绍了Adsp-TS101芯片及其在雷达信号处理方面的应用。该应用系统充分利用了Adsp-TS101高速的运算能力、数据吞吐量大以及易于多片连接,可对数据进行串行处理的特点。文中还讨论了DSP应用过程中的电源设计和功耗问题,因而具有一定的工程指导意义。目前该系统已成功用于某雷达系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)