1 系统需求分析

数字中频是TD-SCDMA基站中的重要组成部分。对数字中频部分性能需求进行量化分析,可以更清楚地认识数字中频在系统中的位置及其对系统性能的影响,为数字中频研发和测试的提供参考。

TD-SCDMA协议中规定,接收机天线口输入有用信号功率在-110~-80 dBm范围内。同时协议中规定,邻道功率最强为-55 dBm的单码道CDMA信号,15 MHz射频带内最强带外阻塞信号功率为最小3.2 MHz,频偏-40 dBm的单码道CDMA信号。ADC入口的最大功率为6 dBm时,可以估算频链路额定增益为40 dB,若接收机射频链路的噪声系数可以做到5 dB,则可以估算ADC输出信噪比应大于74 dB,ADC的有效位宽应大于等于12 b。

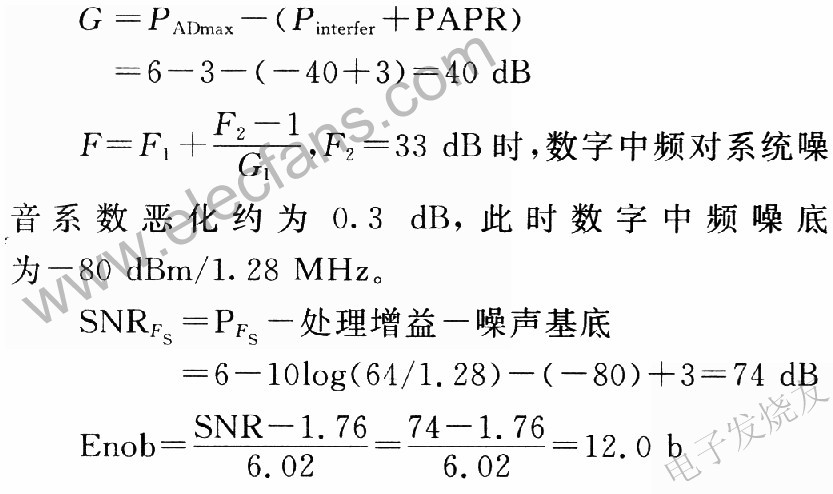

计算过程参考如下方法:

采样时钟抖动(Jitter)和ADC固有的抖动也会恶化信噪比,在大信号输入时尤为明显。根据SNR=-20 log(2πfσt),以采样时钟为100 MHz计算,当射频部分无带外抑制时,链路增益为40 dB,此时Jitter等效ADC输入口噪音功率为-65 dBm,允许的时钟抖动为5 ps。当射频部分对带外阻塞信号有15 dB抑制时,链路增益为55 dB,此时Jitter等效ADC输入口噪音功率为-50 dBm,允许的时钟抖动为20 ps。

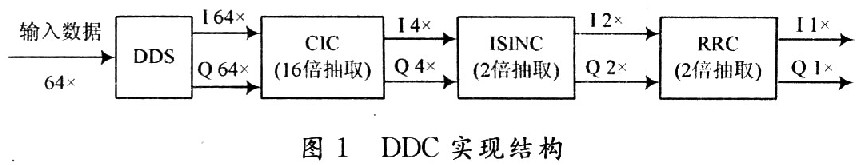

A/D采样信号经过抽取后会混到有用信号带内,因此在射频链路对阻塞信号没有任何抑制的情况下,需由数字滤波器将其滤除。最恶劣情况下阻塞信号会比有用信号强70 dB,因此数字滤波器的远端带外抑制应达到70 dB。滤波器一般选用CIC,ISINC,RRC级联实现,NCO的杂散应小于-80 dB。TD-SCDMA协议中规定,要采用滚降因子为O.22的根升余弦滤波器(RRC)来实现反脉冲成形滤波。图1为一般DDC的实现框图。

2 AD6655的结构和工作原理

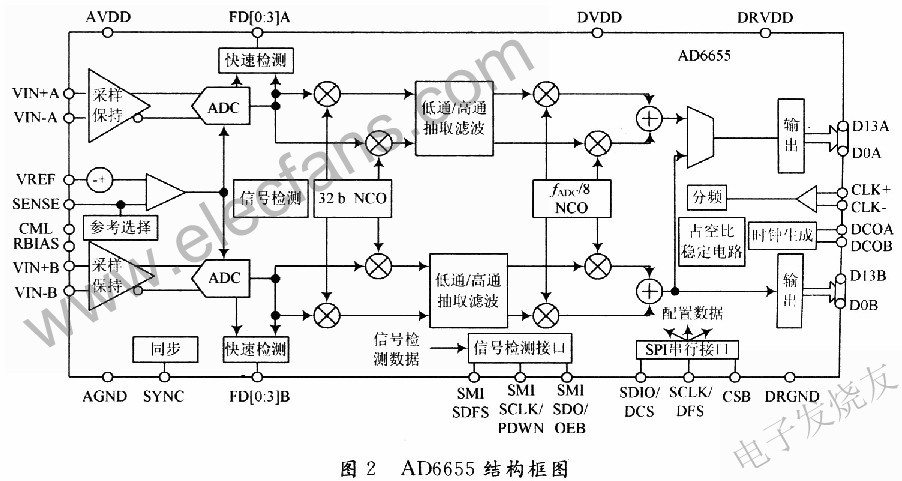

AD6655是Analog Device公司的一款功能强大的中频接收器件。它内置双通道14 b、最高125 MSPS采样率的ADC,宽带DDC,以及功率检测功能。

AD6655具备以下特点:

(1)1.8 V模拟供电,1.8~3.3 V输出供电,有低功耗模式;

(2)双通道ADC:内部参考电压,1~2 V输入电平范围,采样频率最高到125 MSPS,SN

R为71.7 dBc to70 MHz@125 MSPS,SFlDR为85 dBc to 70 MHz@125 MSPS,85 dB的隔离度;

(3)内置ADc时钟占空稳定器,1~8倍的时钟分频;

(4)双通道DDC,包含32位NC0,半带插值滤波,FIR滤波器;

(5)复合信号检测功能。

它的结构框图如图2所示。

此款芯片可以应用在:GSM,EDGE,TD-SCDMA,WCDMA,CDMA2000,IMT-2000,WiMax,LTE等领域。

AD6655虽然是一颗14 b高速ADC,但由于内嵌了抽取滤波器,所以在产业化阶段并不需要严格的进口许可认证,对降低系统成本起到很大作用。

3 AD6655在TD-SCDMA基站系统中的电路设计

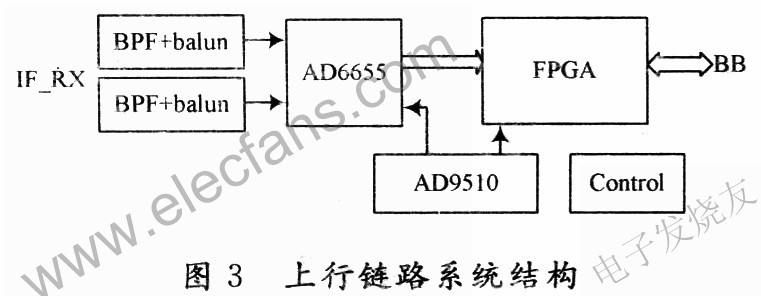

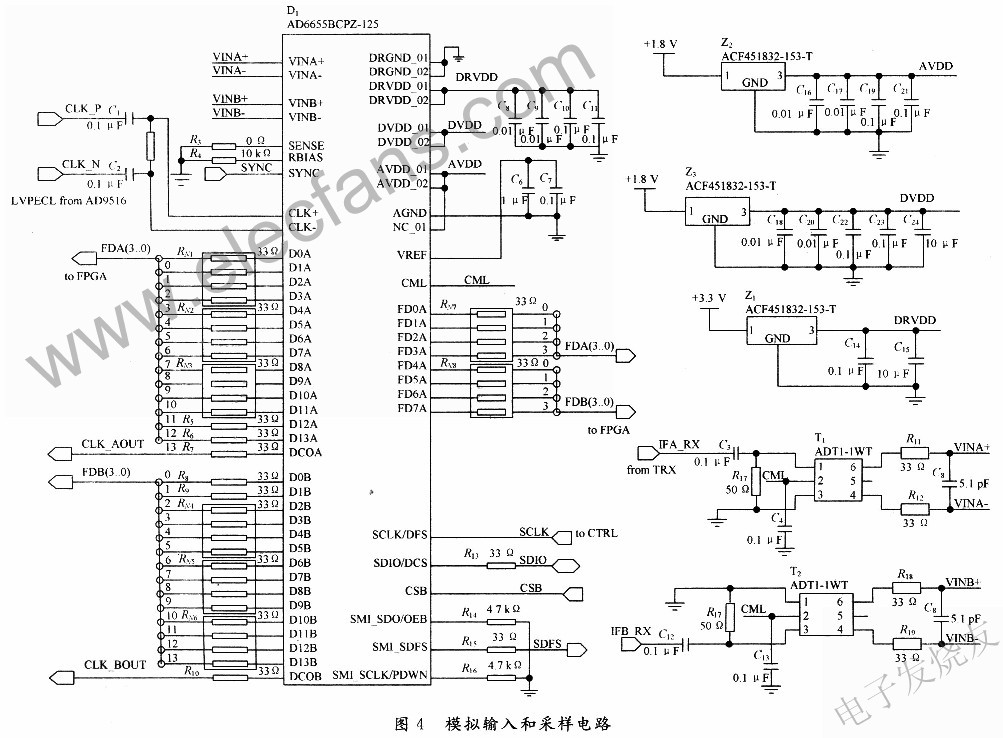

由于AD6655为双路ADC+DDC,所以在多天线基站系统中使用比较方便,例如8天线智能天线系统只需要4片AD6655。为满足采样时钟的Jitter要求,采用AD9510锁定系统时钟并驱动AD6655的采样时钟(LVPECL逻辑),匹配方式为交流耦合。AD6655采用内部参考电压,模拟中频信号由SMA连接器输入后,采用1:4的balun由不平衡输入转换到平衡输入,可以得出中频信号的溢出告警电平为10 dBm左右,系统对模拟中频输入信号的功率要求为小于6 dBm。图3为基站的上行结构框图。

153.6 MHz宽度的模拟中频信号经过A/D采样后,中心频率在30.72 MHz。数据在芯片中会进行进一步的数字下变频转换。进入DDC的输入数据为调制到24×、速率为96×的数据。DDC部分由四大部分组成:NCO,CIC,ISINC滤波器和RRC滤波器。NCO部分完成解调的功能,将数据分成I和Q两路,然后I,Q数据经过完全相同的两个通道进行抽取,分别进行CIC滤波、ISINC滤波器和RRC滤波器,最后将数据抽取到1×,送给基带。

AD6655的控制接口采用3线SPI和控制部分通讯,内部寄存器通过它进行配置和控制。AD6655有几十个寄存器,主要为A/D模式、DDC配置、及同步控制等,芯片上电后由板卡控制单元进行配置。

4 信号链的系统仿真

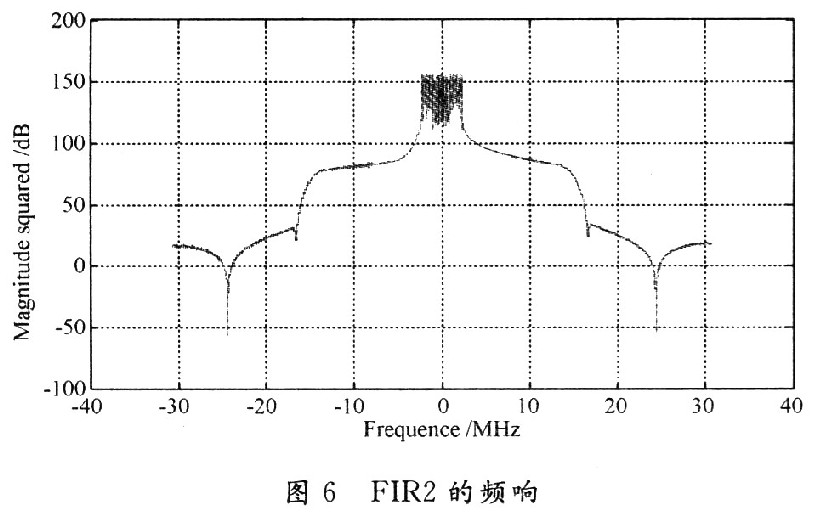

ADC采样后,153.6 MHz中频频点的三载波信号数字化为中心频点在30.72 MHz的信号。由于是实信号,因此在负频率处有其镜像信号。

低中频信号进入数字混频器,转换为多载波0中频信号,同时将实数数据转换为In-phase和Quadrature正交的两部分分量。

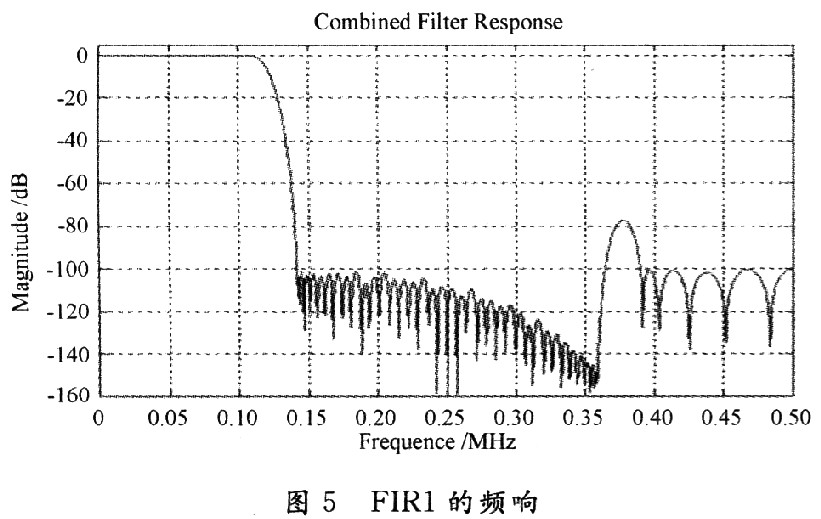

AD6655的第一级滤波器为19阶的半带滤波器,它实现2倍抽取滤波,并且不能被旁路,因此它的带宽也决定了接收链路的最大带宽。器件手册指出最大可用带宽为采样率的11%,在122.88 MSPS采样率下支持的带宽为27 MHz。AD6655还有一个66阶的FIR滤波器,为抵消CIC滤波器对有用信号高频抑制的影响,FIR中加入了Inverse Sinc函数对高频信号进行补偿。

2级滤波器的级联频响如图5所示。

经过2级滤波器,AD6655输出信号的频谱特性如图6所示。

FPGA接收到AD6655的信号,由于已经对信号进行了2倍、或4倍的抽取,所以FPGA的工作频率就可以降低到ADC采样频率的了1/2或者1/4了。这对FPGA的型号选择和降低成本都是有利的。

FPGA需要继续对信号进行滤波和抽取,以达到系统ACS和Blocking要求的带外抑制度。由于AD6655可以对数字远端进行-80 dBc的抑制,那么FPGA只需要对带宽近端进行相应的滤波,通常90阶滤波器可以实现-50 dBc的带外抑制,当然采用分级滤波的方式效果可能更明显,并且一些滤波要在载波分路后进行。

FPGA需要继续对信号进行滤波和抽取,以达到系统要求的ACS和Blocking带外抑制度。由于AD6655可以对数字远端进行-80 dBc的抑制,那么FPGA只需要对带宽近端进行相应的滤波,通常90阶滤波器可以实现-50 dBc的带外抑制,当然采用分级滤波的方式效果可能更明显,并且一些滤波要在载波分路后进行。

5 仿真结果和评价

由以上仿真来看,AD6655可以满足基站上行链路中的应用,信号处理后输出给FPGA,节省了很多FPGA的逻辑单元。在AD6655Demo板和TD-SCDMA数字中频板卡DIFB 3.O进行了实测,测试结果完全符合设计要求。总之,AD6655是一款比较合适的数字中频接收链路的器件,可以应用在3G基站系统中,具有较高的性价比。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)