在工业控制领域,通常有大量的脉冲信号用于控制其他设备或部件的开关或者工作状态切换。这些脉冲信号除了常规计算机系统采用的+5 V接口电平外,还有+12 V、+30 V,乃至更高幅度的接口电平,通常为功率型电流驱动信号。本文提出了一种两级测试系统的设计思路,给出了在较宽的范围内兼容不同接口电平的脉冲信号检测系统的设计方案,采用标准CPCI总线接口设计,具有良好的兼容性和扩展性,适用于产品功能测试或系统集成测试。

1测试系统架构

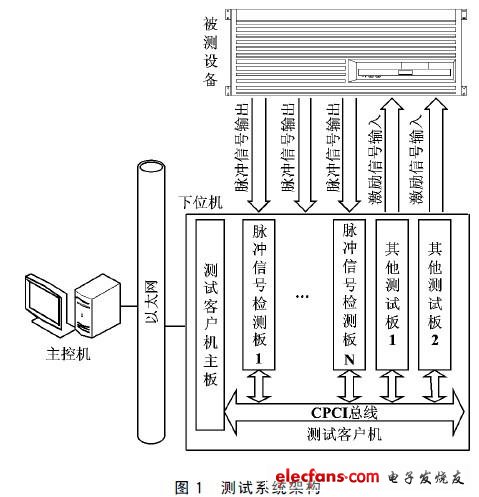

如图1所示,测试系统采用二级(主控机、下位机)结构设计,由主控计算机(即主控机)、测试客户机(即下位机)、局域网、电缆及运行于各设备中的测试软件共同构成。主控计算机属主控机一级,控制测试客户机,测试任务由主控计算机控制完成。测试客户机控制其对应的测试设备可独立完成设备级的功能测试。整个测试系统通过对被测设备施加激励信号并检测其响应输出的方式,实现对被测没备的闭环测试。

脉冲信号检测板是工作于测试客户机中的测试板卡,其主要功能是接收80路外部脉冲信号,测量并记录每路脉冲信号的脉冲宽度及收到脉冲的时间。

2脉冲信号检测板实现方案

2.1总体设计

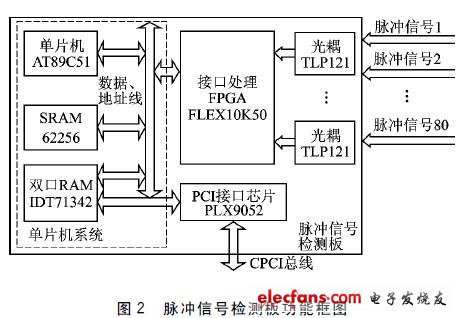

脉冲信号特性为:脉冲持续时间为80~500 ms,偏差为±10 ms;驱动电流不小于200 mA.在产品功能测试及系统集成测试阶段,主要考核脉冲信号功能的正确性,故脉冲信号检测板用于检测脉冲信号的发生时间及脉冲持续宽度,要求测量误差不大于±1ms.如图2所示,脉冲信号检测板的核心部分包括光耦接口电路、接口处理FPGA、单片机系统和PCI接口电路。板卡采用标准的6U尺寸CPCI板卡设计,兼容标准6U尺寸的CPCI工控机。

检测板内部主要数据流向及处理流程为:80路脉冲信号通过光电耦合器(光耦)进行隔离变换,转换成检测板内部5 V电平信号;接口处理FPGA对信号进行采样,并将80路脉冲采样数据组帧缓存;单片机读取FPGA中的采样数据,并判断是否检测到有效脉冲信号,将检测到的脉冲信号打上当前时间标签后发送给双口RAM;工控机软件通过CPCI总线定期访问双口RAM,读取数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)