电子发烧友网核心提示:RS 232接口是现在最常用的一种通信接口。随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性。详细阐述了如何通过FPGA实现RS 232接口的时序逻辑设计。

RS 232接口是1970年由美国电子工业协会(EIA)联合贝尔系统、调制解调器厂家及计算机终端生产厂家共同制定的用于串行通信的标准。它的全名是“数据终端设备(DTE)和数据通信设备(DCE)之间串行二进制数据交换接口技术标准”。该标准规定采用一个25个脚的DB25连接器,对连接器的每个引脚的信号内容加以规定,还对各种信号的电平加以规定。随着设备的不断改进,出现了代替DB25的DB9接口,现在都把RS 232接口叫做DB9。RS 232接口是最常见的一种串行通信接口,普通PC机一般都具有此类接口,其最高通信速率(波特率)为115.2 Kb/s。采用9 600b/s进行数据传输交换的应用较多。通过FPGA实现其时序电路,主要完成发送和接收两部分逻辑电路的设计。

1 发送逻辑电路的设计

1.1 时序近似

RS 232接口可选的波特率如9 600b/s,115.2 Kb/s等同11.059 2 MHz的时钟有着整数倍的关系,但通常情况下提供FPGA的时钟大多采用频率为40~80 MHz,同11.059 2 MHz之间存在一定的时序误差。

例如一个由1个起始位,8个数据位,1个停止位组成,假定串行信号的波特率为9 600b/s,则每个位的时序时间为:

104 166.666 666 666 666 666 666 666 666 67 ns

相当于80 MHz计数器计数到:

8 333.333 333 333 333 333 333 333 333 333 3舍去小数部分。

由80 MHz驱动的计数器产生时序时每个字符误差为4.166 666 666 666 666 666 666 666 666 666 7 ns。这样由10个字符组成的一次发射时序误差约为41.7 ns小于1/1 000可以忽略不计。

1.2 发送时序设计

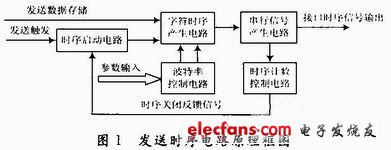

RS 232接口的时序电路由启动电路、字符产牛电路、同步时钟产生电路。波特率控制电路,和时序关闭电路组成。发送时序电路原理框图如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)