摘 要: 以SoC软硬件协同设计方法学及验证方法学为指导,系统介绍了以ARM9为核心的AFDX-ES SoC设计过程中,软硬件协同设计和验证平台的构建过程及具体实施。应用实践表明该平台具有良好的实用价值。

航空系统中的控制系统对数据的安全性、实时性、可靠性及可维修性有极高的要求。在这种环境下,必须使用最具可靠性与实时性的通信链路。航空全双工交换以太网AFDX(Avionics Full-Duplex Ethernet)的开发满足了商业航空应用的需要。AFDX[1]是一种航空电子子系统间进行数据交换的网络标准,它是在IEEE802.3以太网技术的基础上增加一些特殊机制,提供一个具有确定性和可靠性的网络。冗余链路的设置,保证了数据报文传输的可靠性。帧管理机制负责在数据报文发送给应用程序之前检查帧的完整性和管理冗余。

AFDX-ES(End System)是指AFDX的终端系统,主要功能是提供服务,确保提供给应用方的数据具有安全性和可靠性。每一个终端系统与交换机之间不仅有一条直接的双向连接,同时还与另一台交换机之间保持第二条双向连接,确保终端系统具有冗余性。

AFDX-ES SoC是从航电系统总线应用需求出发,规划出以高性能ARM922T处理器为核心、可实现AFDX协议主要功能的高速互联网终端系统芯片。

典型的SoC验证平台通常采用3种体系结构:黑匣子结构、通用现场可编程门阵列FPGA板和开放式结构。开放式结构因其在系统资源使用和扩展上的灵活性,已成为SoC验证平台的主流,典型的平台有加州伯克利大学的BEE、Hardi公司的HAPS和ApTIx公司的MP4CF。BEE和HAPS采用大规模 FPGA阵列,MP4CF则采用现场可编程互联元件(FPIC)技术。在国内一些大学也开发了规模相对较小的FPGA阵列验证平台。

SoC验证所花费的工作量平均占总设计工作量的80%以上,验证已逐渐成为大规模集成电路设计的主要瓶颈。随着我国航电系统大规模芯片设计的快速发展,SoC的规模越来越大,设计与验证流程越来越冗长,如何缩短验证时间、提高验证效率和质量、缩短芯片面市时间, 已是SoC设计领域中最受关注的问题。为了加速SoC的验证,缩短开发周期,有效解决AFDX-ES SoC设计逻辑验证的瓶颈限制,本文提出了用于验证AFDX-ES SoC芯片逻辑功能的FPGA验证平台,采用软硬件协同验证方式,以确保在流片之前对设计进行充分、有效的验证。

1 AFDX-ES芯片架构

AFDX-ES SoC芯片的片上总线采用ARM公司的AMBA(Advanced MicroController Bus Architecture)总线,包括高速总线(AHB)和外设总线(APB)等。AHB总线提供高带宽、低延迟的连接,APB总线为连接具有不同总线宽度和时序要求的外设提供一条途径,避免低性能设备对高性能设备的影响。ARM922T处理器、ES-CCU(终端系统中央控制单元)控制器、PCI总线控制器、SRAM、中断控制器、SDRAM控制器、Flash接口、DMA和测试接口控制器(TIC)挂接在AHB总线上,TIMER、RTC、WDT、串口控制器及通用输入输出接口等挂接在APB总线上,AHB/APB桥接器可以提供两种总线之间的访问控制。

目前基于0.18 ?滋m的复杂芯片一次投片成功率只有35%左右,造成芯片重复投片的主要原因是验证不够充分。SoC设计的验证需要投入的资源已占整个设计资源的60%~80%,如何在流片之前对设计进行充分的验证,已成为整个SoC设计流程的关键。

对于功能复杂、具有高集成度的SoC,要在流片前充分验证,确保流片功能的正确性,构建AFDX-ES SoC设计与验证平台是确保一次流片成功的前提。

2 AFDX-ES SoC设计与验证流程

AFDX-ES SoC设计与验证采用层次化验证的方法,软硬件协同设计与层次化验证由以下4个阶段组成:

(1)IP/模块级仿真验证;

(2)基于芯片虚拟原型的软硬件协同验证;

(3)基于芯片FPGA原型的软硬件协同验证;

(4)物理设计后的版图后仿真。

本文重点描述基于芯片FPGA原型的软硬件协同验证。

3 基于芯片FPGA原型的软硬件协同仿真验证

基于虚拟原型的验证平台可以大量验证设计电路的功能,但是存在验证时间长、速度相对较慢的缺点[5]。因此,一些验证时间比较长的验证项,如大量帧收发的验证、协议验证、 *** 作系统验证等适合在基于芯片的FPGA原型中验证。可以充分发挥此平台的验证特点,尽可能模拟系统的真实应用环境,对于在虚拟原型平台上不便于验证和难以验证的验证项进行快速验证。此阶段的验证可以认为完全等同于芯片的逻辑功能的全面验证。基于芯片FPGA原型的软硬件协同验证的充分验证,一方面可以发现设计中存在的各种问题;另一方面尽可能地将芯片的FPGA原型置身于应用环境下,*价芯片能不能用、好不好用。

3.1 芯片FPGA原型的软硬件协同验证平台的构建

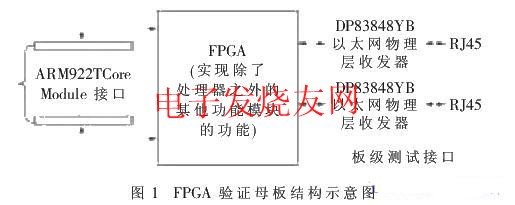

在芯片的FPGA原型构建过程中采用基于ARM922T-

Core Module+验证母板的模式。ARM922T Core Module板卡实现ARM922T处理器的功能,并且提供一组标准的接口;验证母板实现AFDX-ES中除了处理器之外的其他功能模块的功能及其他测试手段。

验证母板上包含了AFDX-ES逻辑单元及外围的辅助测试资源,验证母板的结构如图1所示。

3.2 基于芯片FPGA原型平台的验证程序的开发

此阶段的程序开发主要有4个方面。

(1)对于虚拟原型中使用的基本资源、基本功能及部分系统级功能验证程序,需要移植到FPGA验证平台。由于FPGA验证平台与虚拟原型的验证平台有一定的差异,包括地址空间分配等,需要把原来在虚拟原型平台上的程序做相应的移植。本部分软件支持3.3节完成芯片的基本资源、基本功能和系统级功能的验证工作。

(2)开发典型的AFDX协议验证程序。在虚拟原型验证平台上受验证速度等因素的限制,一些系统级的验证和协议验证必须在FPGA验证平台上实现。本阶段开发的软件完成3.4节AFDX协议的软硬件协同验证;

(3)嵌入式 *** 作系统的移植与应用验证程序的开发。本阶段开发的软件完成3.5节基于芯片FPGA原型的嵌入式 *** 作系统协同验证。

(4)开发典型应用验证程序,本阶段开发的软件可完成3.6节的典型应用验证。

3.3 基于芯片FPGA原型平台基本功能验证

基于FPGA原型的验证要对虚拟原型验证平台的所有验证项进行验证,保证虚拟平台的所有验证内容在真实环境中也是正确的[6]。首先要进行的是资源和功能的验证。在此阶段主要还是使用虚拟原型阶段开发的验证程序对于资源和功能进行验证。但是需要注意的是,由于受ARM922TCore Module的限制,虚拟原型和FPGA原型的地址空间分配等有所不同,需要根据具体情况进行相应的修改。

在此阶段,对每一个设计模块都必须进行详细的测试验证,尤其是验证在真实的硬件环境中各个模块的特性和功能是否满足要求。针对核心模块ES-CCU还需要进行大量帧收发的验证,确保在大数据量传输时该功能模块无缺陷。

3.4 基于芯片FPGA原型AFDX协议的软硬件协同验证

芯片实现了AFDX协议功能,在实际应用中必须开发相应的协议软件以满足系统要求,在设计阶段需要开发协议软件进行软硬件协同验证。主要包括驱动层软件和协议层软件。

驱动软件实现设备管理并提供用户或 *** 作系统访问网络通道硬件设备的接口,设备驱动程序采用结构化的设计思想。遵循Linux、Windows等系统的程序设计规范,提供一个通用的与设备无关的程序结构,方便系统移植和维护。按照通用设备结构,为上层用户提供一组通用的设备管理和通信函数。驱动层软件主要包括初始化软件和接口函数。初始化软件包括上电初始化、通信协议初始化、DMA初始化配置、PCI初始化配置、协议初始化配置和中断初始化等初始化过程。

协议层软件主要实现针对协议层要求对数据进行分片、打包等转换,并对从MAC端口接收的数据进行完整性检查和余度管理,完成数据与包头的分离、校验和计算、UDP协议类型提取等 *** 作,为片上处理器进行协议栈处理提供必要信息。

3.5 基于芯片FPGA原型的嵌入式 *** 作系统协同验证

芯片FPGA原型的验证能够最直接和全面地验证设计的正确性和完备性,是虚拟原型验证通过之后最接近真实硬件设计的验证。虽然完成了模块级、系统级的验证程序对片上各个模块之间的互动 *** 作进行模块级、系统级功能验证,但这种方法仍然很难保证验证的充分性。

在此情况下,往往采用基于嵌入式 *** 作系统的系统级软件,从资源管理者的角度进行功能的充分验证。

嵌入式 *** 作系统作为嵌入式系统的灵魂,对整个系统进行硬件资源管理、多任务协调调度、任务间同步和通信、存储管理、设备管理等。在SoC验证中,通过运行嵌入式 *** 作系统及基于 *** 作系统的应用程序,模拟真实的软件应用环境;通过验证平台的搭建,能够移植 *** 作系统和各种实际应用软件,更加真实地模拟应用环境, *** 作系统的移植和运行能够更高效地覆盖硬件设计IP及互联的验证项,实现较高的验证覆盖率。可以在芯片的设计阶段发现 *** 作系统是否能够对硬件资源进行管理、能否有效地进行任务管理等问题,能否对设计中各模块功能以及系统功能进行更为有效的验证,尽早地发现SoC硬件设计中的缺陷,确保设计的正确性和可靠性,为芯片的充分验证提供了有效手段。同时,为流片后的芯片测试及应用工作提供了一个良好的测试平台和应用软件的开发平台,加速SoC应用开发的进度,加速芯片推广和尽快上市。

日益复杂的应用需求,加快了嵌入式 *** 作系统的发展。目前国内外已有几十种商业化 *** 作系统可供选择,如VxWorks、WinCE等。在同一硬件平台上可以运行不同的嵌入式 *** 作系统,但必须根据自己的硬件平台和应用场合将某种 *** 作系统进行定制和代码修改,使其能够运行在该硬件平台上,这个过程就是 *** 作系统的移植。在明确验证了芯片的基本硬件资源以后,移植尽可能多的嵌入式 *** 作系统至SoC上,确保验证的充分性。在AFDX-ES设计中,在FPGA原型验证环境下移植了VxWorks嵌入式 *** 作系统,并编写大量上层应用程序来对SoC硬件设计进行了详尽的验证。

VxWorks是美国风河公司设计开发的一套具有微内核(最小为8 KB)、可裁剪的高性能实时 *** 作系统(RTOS),支持广泛的网络协议。其在军事、航天、通信、工业控制等诸多方面应用广泛,并已成为嵌入式领域使用最多的 *** 作系统之一。基于FPGA平台的VxWorks系统移植验证,需要建立开发环境,在PC机上安装VxWorks集成开发环境Tornado2.2 for ARM,采用宿主机目标机交叉开发,以网口作为内核下载通道。编写一个可靠的BSP软件包,是进行VxWorks *** 作系统移植工作的重要部分,直接决定了 *** 作系统移植能否成功。设计中根据具体的硬件点,首先配置一个能生成最小内核的BSP包,包括中断处理程序、定时器驱动,同时为了方便调试,还加入网口驱动,以便启动WDB调试工具[10]。在成功运行最小内核以后,以此BSP包为基础添加基于AFDX-ES芯片上其他模块的驱动程序,以达到对系统的充分验证。

通过运行VxWorks嵌入式 *** 作系统,对片上资源进行管理以及各功能模块进行功能调用,验证了AFDX-ES芯片各IP模块的工作情况及各IP模块在系统中相互配合工作的情况,尽早地发现了SoC硬件设计中的缺陷,确保了设计的正确性和可靠性。由此,在SoC上移植嵌入式 *** 作系统可谓SoC的设计中一个优秀的测试向量集。

3.6 基于芯片FPGA原型的典型应用验证

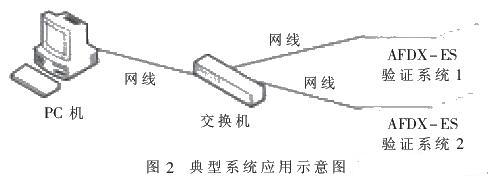

为了进一步验证设计的SoC是否满足系统的应用需求,利用搭建的芯片FPGA原型构建了一个典型的系统应用环境,对于AFDX-ES进行了典型系统应用验证。在此系统中使用了一台AFDX交换机。此阶段的验证一方面通过验证证明所设计的SoC可以与交换机进行通信;另一方面此阶段所开发的验证原型系统也是所设计SoC的一个系统解决方案。

图2所示的应用验证是一个典型的应用验证环境。在此基础上,使用了一台AFDX交换机、2块AFDX-ES验证板和1台PC机。PC机与AFDX交换机连接,可作为服务器使用,2块AFDX-ES验证板都连接到交换机,验证系统1可以通过交换机与系统2通信,同时,也可以通过驻留在PC机上的监控软件检测数据交换状态。通过上述验证表明所设计的AFDX-ES可以与交换机互相通信,满足系统应用需求。

为了适应我国航电系统大规模芯片设计的快速发展,解决验证规模的瓶颈限制,本文提出了以ARM9为核心的AFDX-ES SoC软硬件协同验证方法、流程和平台。整个验证过程基于FPGA原型,对设计的基本功能进行了充分验证,完成了协议所要求的最基本的数据处理机制的验证,验证软件可以很好地应用在流片后的系统应用中,同时利用原型平台构建了与交换机通信的典型应用环境,并在此环境中开发了相应的程序,实现了交换机的通信验证。此阶段开发的应用程序和原型系统可以应用在流片后的系统中。

本文介绍的软硬件协同设计验证方法、流程、平台能在流片之前对设计进行充分、有效的验证,在项目的实践中取得了良好的效果,对于类似的SoC协同验证有很好的参考价值

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)