嵌入式设计人员面临的最大挑战之一就是界定系统的性能需求。用以确定实际性能需求所需的信息要么无法获取,要么难以获得。最精确的估算有时也会因无法预料的计算负荷而失效。分析通常会指出,对于数据处理需求而言嵌入式处理系统的成本效益太低。因此,系统设计人员高度渴望拥有可扩展的能够适应性能需求潜在变化以及能够执行高性能数据处理的架构。而在FPGA内部实施的控制平面/数据平面处理架构就能够有效满足上述要求。

什么是控制平面/数据平面处理?为什么您的下一代嵌入式系统可能会需要它?

在无法用软件完成所有处理工作的系统中,设计人员可以通过多种途径来获得其他性能。他们可以采用对称或者非对称处理配置的多处理器;使用硬件协处理器;或者将数据处理任务拆分给一个或多个专用处理单元——就像在控制平面/数据平面内进行处理一样。

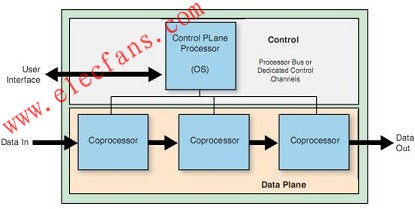

在这种编程方式下,数据处理被分成两个不同的平面。控制平面代表着对性能影响不大的算法元素,比如管理性任务、用户界面和 *** 作系统功能。同时,数据平面代表着数据在系统中的流动,例如视频流或音频流及其处理。在数据平面上,设计人员采用诸如流水线这样的技术来增强数据吞吐能力。控制平面/数据平面处理的典型应用包括流视频、网络包处理以及高速信号处理。

让我们来近距离观察一个涉及流数据实时处理的控制平面/数据平面应用。我们将面临高清视频流特有模式的识别。该实要求混合使用高性能数据处理和包含嵌入式微处理器的控制功能的多种应用的典型代表。

720p/60Hz的HD视频流的像素频率为74.25MHz。这就要求222.75MB每秒的处理速率。假定采用2.5GHz的双核双指令处理器来处理该数据,最佳的指令率为10G指令每秒。这样的处理器可针对所处理数据的每一字节执行22.4条指令。对某些应用而言这已经足够了,但22.4条指令表明所能处理的数据非常有限。复杂的视频处理功能,比如内核卷积(kernelconvoluTIon)、噪音消减和其他过滤功能需要更高的指令执行效率。本文的解决方案准备在数据平面上创建并行或流水线处理单元。

HD视频处理是一种可以把问题划分为控制平面和数据平面予以高效处理的常见的现实应用。作为一种高度并行处理单元,FPGA在本例中负责视频处理,同时由FPGA内部的中等性能处理器负责视频处理流水线。该处理器可专用于单个应用,也可以运行诸如Linux这样的 *** 作系统。最终形成的硬软件混合实施方案可以把处理交付给能够进行最佳处理的部分,实现低成本、高性能数据处理解决方案。图1显示的是典型的控制平面/数据平面系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)