来源:微计算机信息,作者:王恒心,熊庆国,王鑫,陈礼敏

VGA(视频图形阵列Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

目前 VGA技术的应用还主要基于 VGA显示卡的,而在一些既要求显示彩色高分辨率图像又不使用计算机的设备上,VGA技术的应用却很少。本文对基于 FPGA/CPLD的嵌入式 VGA显示的实现方法进行了研究。

基于 FPGA/CPLD的嵌入式 VGA显示系统,可以在不使用 VGA显示卡的情况下实现 VGA图像的显示和控制。该系统具有成本低、结构简单、应用灵活的优点。

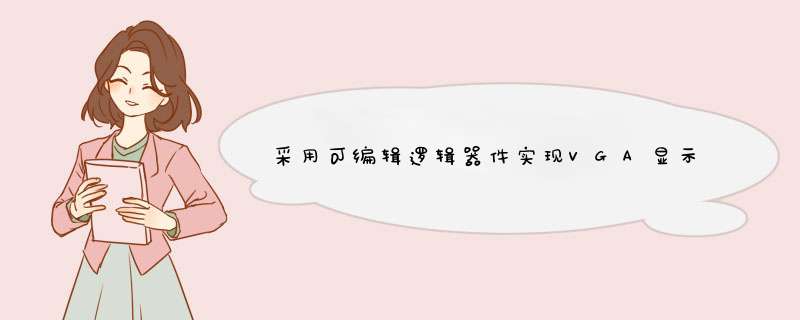

1 基于 FPGA/CPLD的嵌入式VGA显示系统简介

VGA接口芯片采用了 ADV7125,该芯片是美国 ADI公司生产的高速视频数模转换芯片,其像素扫描时钟频率有 50MHz、140 MHz、270 MHz、330MHz四个等级。ADV7125在单芯片上整合了三组 8位高速 D/A转换器,可以分别处理红、绿、蓝视频数据,特别适用于高分辨率模拟接口的显示终端和要求高速 D/A转换的应用系统。 ADV7125的输入及控制信号非常简单:3组 8位的数字视频数据输入端,分别对应 RGB视频数据,数据输入端采用标准 TTL电平接口;4条视频控制信号线包括复合同步信号 SYNC、消隐信号 BLANK、白电平参考信号 REF WHITE和像素时钟信号 CLOCK;外接一个 1.23 V数模转换参考电压源和 1个输出满度调节。只有 4条输出信号线:模拟 RGB信号采用高阻电流源输出方式,可以直接驱动 75Ω同轴传输线。

2、模块划分与模块功能定义

FPGA中包含了四个工作模块: VGA时序发生器模块、VGA图像显示调色板模块、数据存储器和数据读写控制器。由于 ADV7125内部没有颜色的转换器 ,所以当数据存储器中的数据为 YUV信号时,就要把 YUV信号转换成 RGB信号,这一功能就是由 VGA图像显示调色板模块完成的,当显示数据为 RGB信号时,数据可以直接传输到 ADV7125,不需调色板进行颜色转换。数据存储器和数据读写控制器解决了显示数据的来源和数据的存储。用 FPGA对图像进行存储和整理,并产生驱动电路需要的各种控制波形由视频控制器对颜色缓冲器进行扫描,其中视频控制器可以读取像素颜色,用这些颜色来控制输出设备的亮度。

VGA时序发生器模块产生显示器所需的时序,这是完成设计的关键,时序稍有偏差,显示必然不正常,甚至会损坏彩色显示器。

3、 VGA时序分析

显示器采用光栅扫描方式,即轰击荧光屏的电子束在 CRT(阴极射线管)屏幕上从左到右(受水平同步信号 HSYNC控制)、从上到下(受垂直同步信号 VSYNC控制)做有规律的移动。光栅扫描又分逐行扫描和隔行扫描。隔行扫描指电子束在扫描时每隔一行扫一线,完成一屏后再返回来扫描剩下的线,与电视机的原理一样。隔行扫描的显示器扫描闪烁的比较厉害,会让使用者的眼睛疲劳。目前微机所用显示器几乎都是逐行扫描。逐行扫描是指扫描从屏幕左上角一点开始,从左向右逐点进行扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;当扫描完所有行,形成一帧时,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行行场消隐,开始下一帧的扫描。

完成一行扫描所需时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描所需的时间称为垂直扫描时间,其倒数为垂直扫描频率,又称刷新频率,即刷新一屏的频率。常见的有 60Hz、75Hz等。

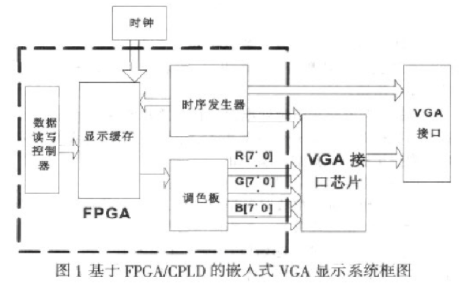

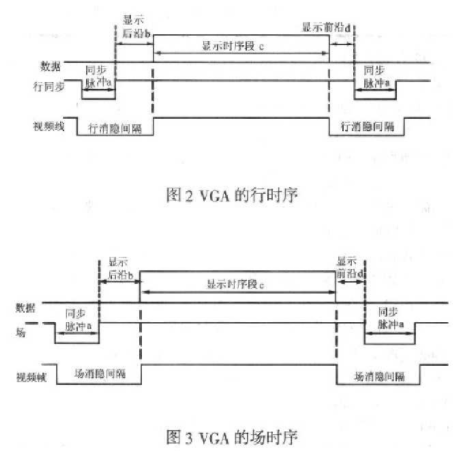

VGA显示器要正确显示图像关键还是如何实现 VGA时序。视频电子标准协会( VESA, Video Electronics Standards AssociaTIon)对显示器时序进行了规范。 VGA的标准参考显示时序如图 2、图 3所示。行时序和场时序都需要产生同步脉冲(Sync a)、显示后沿 (Back porch b)、显示时序段(Display interval c)和显示前沿 (Front porch d)四个部分。 VGA工业标准显示模式要求:行同步、场同步都为负极性,即同步头脉冲要求是负脉冲。

VGA的行时序如图 2所示:每一行都有一个负极性行同步脉冲( Sync a),是数据行的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿 (Back porch b),在显示时序段(Display interval c)显示器为亮的过程,RGB数据驱动一行上的每一个象素点,从而显示一行。在一行的最后为显示后沿(Back porch b)。在显示时序段( Display interval c)之外没有图像投射到屏幕时插入消隐信号。同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)都是在行消隐间隔内( Horizontal Blanking Interval),当行消隐有效时, RGB 信号无效,屏幕不显示数据。

VGA的场时序与 VGA的行时序基本一样,如图 3所示,每一帧的负极性帧同步脉冲(Sync a)是一帧的结束标志,同时也是下一帧的开始标志。而显示数据是一帧的所有行数据。

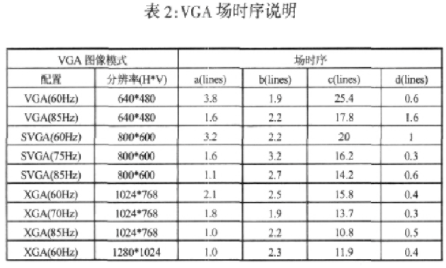

几种常用的时序参数如表 1和表2 所示,首先,根据显示器的性能选择一种合适的VGA模式,然后由象素时钟频率和图像分辨率计算出行总周期数,再把表 1和表 2中给出的 a、 b、c、d各时序段的时间按照象素计数脉冲源频率折算成时钟周期数。在 FPGA/CPLD中用计数器和触发器,以计算出的各时序段时钟周期数为基准,产生不同宽度和周期的脉冲信号,再利用它们的逻辑组合构成图 2和图 3中的 a、b、c、d各时序段以及 ADV7125的空白信号 BLANK和同步信号 SYNC。

一个示例就是 60Hz时 1280×1024分辨率显示的 VESA标准,在 60Hz时,屏幕每

16.67毫秒更新一次。这个标准制定了帧大小,用它来定义分辨率和回扫次数之间的关系。对于分辨率大小为 1280×1024来说,帧的大小为 1688×1066,这个大小与像素时钟(Pixel Clock)有关,所谓像素时钟就是对像素的刷新频率。像素时钟为 1688×1066×60Hz 或者 108 兆 Hz(MHz)时,每个像素的刷新频率也就是大约 9.26纳秒,那么行频就为 60×1066=63960 行/秒,也就是用显示器的帧率乘以扫描线数量。可以用帧大小得到纵向回扫次数,为了得到纵向同步长度(Sync Length),可以从纵向帧大小减去纵向分辨率,也就是 1066-1024=42。这样,纵向回扫花费的时间和在屏幕上绘出 42 条线的时间相同,对于纵向回扫来说需要的时间为 42×1688×9.26 纳秒(656 微秒)。

在显示时序段( Display interval c),数据读写控制器从数据缓存区读取像素颜色,用这些颜色来控制输出设备(显示器)的亮度。一帧图像就准确的显示到 VGA显示器上。

4、 VGA显示器在雷达图像显示中的应用

最初,雷达显示器到重要作用,在于使雷达接收机到数据以一种可视的形式表现出来。 *** 作员可以轻易而精确地检测目标的出现,提取目标的位置信息。随着数字信号处理和数字数据处理的进步,越来越多的检测和信息提取过用电子方法自动完成,因此 *** 作员的任务越来越少。现在雷达显示器更像电视监视器或计算机显示器,可以显示完整的连续场景。

雷达获取的信息是径向圆扫描方式属极坐标方式,所以早期船用雷达显示器是一种平面位置显示器,用极坐标表示,采用径向圆扫描方式,在这种扫描方式中,荧光屏上扫描线线径向扫描的数率取决于量程的大小。扫描线选转的速度取决于天线的转速。物标回波的亮度取决于回波视频的信号的幅度。物标回波及各种符号视频在屏上只能是天线每转一圈才能亮一下,在整个平面上亮度不均,且量程小,回波亮度越低,容易丢失小目标。精确保存物标距离信息非常勉强。目标分辨力差,在屏上画其他符号十分麻烦、困难,且符号量有限。

随着VGA显示器广泛应用,VGA显示器也开始应用在雷达显示上,但VGA显示起的扫描方式是从左到右到扫描和从上到下的帧扫,属于直角坐标的方式,而雷达获取的信息是径向圆扫描方式属极坐标方式,所以要实现雷达数据的 VGA显示首先要将雷达的极坐标信息转换成直角坐标信息存入存储器,再以直角扫描的方式从存储器中读出并显示出来。

VGA显示器可以将来自其他传感器得信息 ,例如其他雷达 :空中交通管制雷达应答系统 (ATCRBS) 、军用敌我识别 (IFF) 、低亮度 TV、前视红外 (FLIR),避免碰撞系统或来自民用或军用数据链的信息 ,都能组合到显示器上 。除已处理雷达视频和原始视频外 ,雷达观测的区域地图及文字数字信息和图形也能添加到 VGA显示器上。。

5、总结

VGA显示器在雷达应用中的优点与平面位置显示器相比,VGA显示器的在雷达图像显示上有了更大优势:

1)克服了平面位置显示器整个平面上亮度不均的缺点。实现了高亮度显示

2)避免显示器的图像的闪烁现象,

3)便于彩色显示

4)便于采用计算机显示终端技术

5)降低了成本,提高了可靠性

本文作者的创新点:在本设计中采用了 1280*1024的高分辨率显示 ,克服了早期低分辨率 VGA显示器雷达图像分裂和定位精度低的缺点 。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)