(来源:微计算机信息,作者:孙世国, 陈 帅 ,陈 倩 ,张恒威 )

1.引言

SPI-4.2(System Packet Interface)是 OIF(OpTIcal Internetworking Forum)定义的局部高速总线标准,用于 PHY层芯片到链路层芯片的 10Gbps信号传输。主要应用有 OC-192 ATM、Packet over SONET/SDH(POS)、10Gbps以太网等。

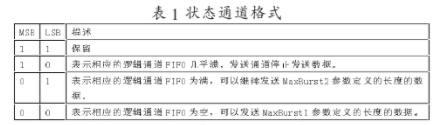

SPI4.2接口分为数据通道和状态通道。数据通道最多分成 256个逻辑通道,16bit位宽,采用 LVDS信号电平,按照 cell格式传送数据,cell的长度为 16字节的整数倍,可随意配置,根据网上流量的分析,一般配置成 128字节。每个 cell都是以控制字开始的,控制字一共16bit,包含逻辑端口号、报文起始标志位、报文结束标志位、控制字交验等信息。状态通道传输对端反馈的逻辑通道接收 FIFO的状态,2bit位宽,LVTTL或者 LVDS信号电平,一般采用 LVTTL信号电平。状态通道的数据结构为 Calendar[0:n],n最大为256,长度一般与逻辑通道数对应,Calendar[n]表示逻辑通道 n的接收FIFO状态。数据通道根据状态通道提供的信息控制数据的发送过程。状态通道有四种状态信息,如表 1所示:

在实际的系统设计中,商用芯片不一定能够满足需要,因此需要使用 FPGA(Field Programmable Gate Array)。本设计采用 Altera的 StraTIx II系列 FPGA和 RMI公司的多核处理器 XLR732,Intel公司的网络处理器 2805实现 SPI4.2接口。

2.2805简介

2805是 Intel推出的高端 NP(Network Prosser),能够处理 10Gbps线速转发的以太网、POS、ATM等数据流量,能够实现分类、NAT、ACL、多播、流量管理等功能。 2805内部集成一个32-bit、RISC内核、高性能的 XScale处理器,用于系统的配置管理和路由表项的维护,最高工作主频750MHz;16个可编程的、有 8K代码空间的微引擎,每个微引擎含有多个硬件线程,用来处理通信系统中的数据转发,最高工作主频 1.5GHz。外部集成了 PCI接口,可以工作在 64bit/66MHz模式;SPI4.2接口,工作频率为 311MHz~500MHz;3个LA-1接口,工作频率为250MHz;4个 RDRAM接口,工作频率为 800MHz~1200MHz。

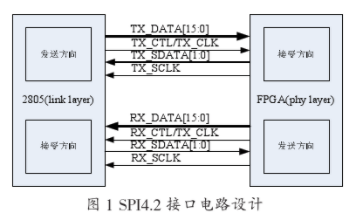

3.FPGA和 2805之间的 SPI4.2接口电路设计

图 1描述了 FPGA和 2805之间的 SPI4.2接口的硬件连接框图,信号定义以 2805为参考点。其中 TX_DATA[15:0] 、TX_CTL、TX_CLK和 RX_DATA[15:0] 、RX_CTL、RX_CLK是 LVDS信号电平,工作在 350MHz;TX_SDATA[1:0] 、TX_SCLK和 RX_SDATA[15:0] 、 RX_SCLK是 LVTTL信号电平,工作在 87.5MHz,四分之一于数据通道时钟频率。

具体信号定义如下所示:

TX_DATA[15:0]:发送数据, 16bit位宽, burst方式传输数据, DDR工作模式(时钟上升沿和下降沿都采样);

TX_CTL:传输控制信号,高电平表示 TX_DATA[15:0]传输的是控制信息,低电平表示 TX_DATA[15:0]传输的是数据;

TX_CLK:发送时钟,随路,是发送数据的参考时钟。

接受方向的信号定义与发送方向的信号定义完全相同,但是方向相反。

4.FPGA的 SPI4.2接口模块设计

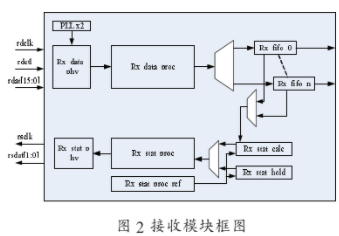

图 2为 FPGA的接收通道逻辑框图,上半部分是数据通道,下半部分是状态通道。由于 SPI4.2接口的数据传输是 DDR模式的,rdclk经过 FPGA内部的 PLL模块做倍频处理,然后送给 Rx_data_phy模块,该模块根据时钟采样 rdat [15:0]上的数据。Rx_data_proc模块将接收的数据按照 cell头中的逻辑端口号,分别放入不同的 Rx_fifo中。一个 Rx_fifo对应一个逻辑通道,每个 Rx_fifo都会生成一个状态信号,标示其“空”状态或者“满”状态, Rx_stat_calc模块根据各个 Rx_fifo的状态信号生成 Calendar信息,由状态通路发送出去,用来流控 2805的发送过程。Calendar也可以由软件设置,通过 Rx_stat_proc_ref下发给 Rx_stat_calc。

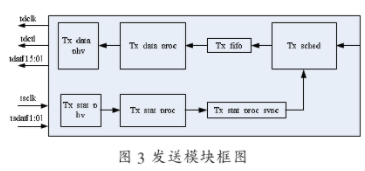

发送模块与接收模块不同,如图 3所示,发送模块的 Tx_fifo只有一个,即所有的逻辑通道公用一个发送缓存区。这主要是由于 FPGA内部的布线资源和 RAM资源有限,同时这种发送端共享 FIFO、接收端分通道 FIFO模式不影响使用,能够实现分端口的反压。

发送端通过 Tx_stat_phy模块接收 Calender信息,经过 Tx_stat_proc模块和Tx_stat_proc_sync模块处理,送给 Tx_sched调度模块,Tx_sched解析出各个逻辑通道的反压情况,然后将各个通道的数据发送到 Tx_fifo中,然后经过 Tx_data_proc模块和Tx_data_phy模块发送出去。

5.结果 本设计在 Altera的 StraTIx II系列FPGA,EPM2S90上得到验证,与 Intel的 2805配合共同完成某通信设备的高速转发单板的设计。

6.结束语

本文介绍了 SPI4.2接口在可编程逻辑器件 FPGA上的实现方法,并通过实际电路验证FPGA与 IPX2805之间通过 SPI4.2接口互通的功能。由于商业芯片的限制,有时只有 FPGA才能满足系统设计的要求。相对于开发ASIC,使用 FPGA使整个设计电路简单、灵活、成本低、方便调试和修改, 大大缩短开发周期。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)