今年国际消费类电子产品展览会(CES)上展出的众多令人难以置信的电子产品再度让我惊叹。产品涵盖各种最新一代设备,从超薄笔记本电脑到功能强大的平板电脑、神奇的二合一移动电脑,再到发展飞速的智能手机等不一而足。无处不在的“物联网”(IoT)受到越来越广泛的关注。简单来说,它不是一台电脑,而是通过互联网进行通信的任何设备。在众多IoT产品中,各种穿戴式设备(包括智能手表和健康与健身追踪器)作为移动设备的后起之秀脱颖而出。

不过,智能手机仍以较大的利润优势占据了移动市场的最大份额,无疑成为推动整个移动市场发展的领头羊。这类产品的核心部件是一个应用程序处理器单元(APU),典型示例就是片上系统(SoC)设计。

应用处理器十多年前,Texas Instruments(TI)在其OMAP(开放式多媒体应用平台)设备的产品线上首次使用了APU这一术语。当时,TI正在为未来的集成方向与Intel一较高下:即芯片级别上的集成还是封装级别(也称作系统级封装或SiP)上的集成。Intel声称,芯片级制造更适合通过在封装组合阶段堆叠单个集成电路芯片来集成不同的功能,包括存储器、数字处理和模拟电路。

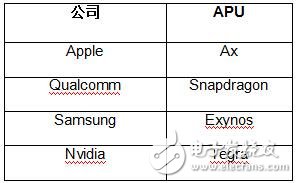

遗憾的是,在相继推出五代OMAP设备后,TI因市场竞争过于激烈而在2012年决定终止开发OMAP系列产品。这是 TI认可现实的表现。只要想想现如今所有大型半导体公司都在设计属于自己风格的AP就不言而喻了。表1列出了这一领域的主要竞争对手。

表I:提供专有APU的主要公司

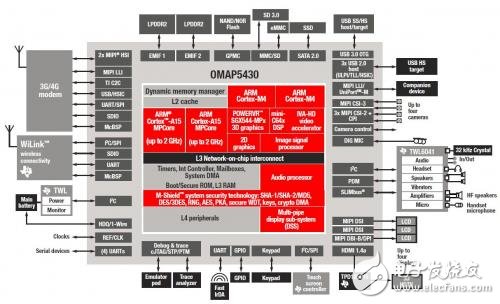

典型的APU可将多个ARM内核、多个图形处理单元(GPU)、较大片上缓存存储器、用于与片外DRAM进行通信的内存控制器、音频和视频解码器(和编码器)以及USB主控制器集成到单一芯片上。此外,它还具有众多其他数字和模拟电路的功能。

图1 代表新式APU的方框图。

图1:Texas Instruments的OMAP5方框图[来源:ICFPT 2014主题演讲,“MegaLUT时代的逻辑仿真:摩尔定律完胜兰特法则”,Mike Butts]

APU案例分析

一家大型移动半导体公司设计出一款可支持创建各种设计尺寸(从百万门到亿万门)的模块式应用处理器。

通常情况下,该公司可为其客户群提供AP和相关系统软件,以作为开发工具包的一部分用于设计新一代移动产品。这些工具包可以帮助客户提早访问工作芯片和软件,加快其开发 片上系统(SoC)和嵌入式应用程序软件的速度,并助其在芯片制造出来之前就能推出新产品,从而在竞争中占得先机。

为应对异常激烈的市场竞争,该公司不得不采用新方法来缩短产品开发周期。而最重要的决策就是使硬件和软件开发流程齐头并进。具体来说,需要为系统软件开发团队提前提供新一代处理器的原型,以帮助其在制造实际芯片之前开始开发 *** 作系统(OS)增强功能和驱动程序。为实现这一目标,公司选择了硬件仿真解决方案。

和大多数复杂集成电路(IC)的开发人员一样,工程师们采用寄存器传输级(RTL)仿真来验证组成最终AP设计的知识产权(IP)模块。然而,在全芯片级仿真上执行集成级测试的效率不高。当设计超过1亿逻辑门时,芯片级仿真的性能达不到每秒一个周期,这对于启动O/S或运行实际应用软件是远远不够的。因此,一旦芯片的基本功能在仿真中经过验证,设计就会被转移至性能可达兆赫(MHz)的硬件仿真平台上。

芯片设计团队使用硬件仿真系统进行处理器验证,而软件开发团队则使用硬件仿真系统验证底层系统软件。一旦全芯片的RTL代码可供使用,整个设计会转移至一个高容量高性能的硬件仿真系统中,这一系统可为完整的系统级验证提供最高10亿门的容量。系统级原型可在所有软件开发小组中共享,用于本地应用程序的开发和验证。

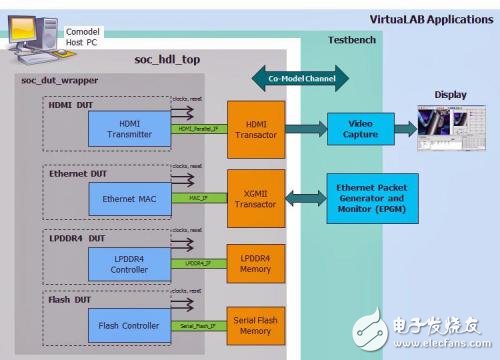

与传统原型相比,这一硬件仿真系统具有诸多优势。举例来说,整个设计都包含在其硬件及其相关联的PC中,无需目标板,也免去了外部电缆、电平位移器和速度适配器。公司使用Mentor Graphics虚拟实验室(VirtuaLAB)提供的各种功能(包括相机传感器、LCD显示屏、外部设备和多媒体接口)来替代物理目标系统。在这种环境下,主机与硬件仿真器设计基于事务级接口进行连接。参见图2。

图2:适用于无线应用程序的VirtuaLAB方框图

该环境是在线电路仿真(ICE)的软件实现方案,被测设计(DUT)由O/S(例如Linux或Windows)使用驱动程序、应用程序和软件堆栈来驱动。这种方法无需创建软件工程师们无法理解的硬件验证测试平台(如 SystemVerilog)。因此,设计师们可以创建能够让软件工程师充分理解的场景和环境。

诸如Mentor Graphics的CodeLink等软件工具可替代JTAG硬件(甚至虚拟JTAG)执行非侵入式调试。在APU中的多处理器环境下,无论何时通过JTAG在一个处理器上执行软件调试,该处理器都会暂停,并且需要运行额外的 JTAG周期,强制该处理器与其他处理器不再同步。而运行同步调试会话会让更多的处理器变得不同步,这样只会雪上加霜。这是由于这种软件只能以被动的方式追踪数据,因此,采用基于硬件仿真的多处理器软件调试更为稳健。硬件仿真系统以兆赫的速度运转,同时表现出与成品芯片一致的行为方式。

除了使系统原型在本质上变得更加可靠外,硬件仿真系统的独立环境无需人为干预即可连接/断开外部设备。而最明显的优势是,全球各个硬件和软件开发团队可以随时随地共享同一个系统,24/7全天候进行不同的设计工作。例如,一个地方的SoC硬件设计团队可以在白天使用该系统进行硬件验证。到了晚上,另一个地方的其他团队可以下载不同的设计并使用相同的系统进行软件开发。这样,硬件仿真系统可以保持24/7全天候运行状态且无需安排本地维护人员看守。

以前,开发团队会使用传统的现场可编程门阵列(FPGA)原型系统且通常需要花费数周的时间才能让设计在系统中正常工作。而诸如多FPGA分区、时钟分布、内存映射以及总线处理等 *** 作都需要人工介入。当不可避免地要更改设计时,团队就必须从头开始整个映射过程,且不得不耗费数周的精力确保修改后的设计能够在 FPGA 软件上正常工作。一旦原型开始正常工作,下一待攻克的难题就是调试。有限的内部可见性和不断变更的测试点需要进行大量的返工。因此,往往需要一个庞大的工程师团队来支持这一单一的原型设计项目。

结论转向基于硬件仿真的方法后,开发APU的公司可以在几天内把设计搬移到硬件仿真平台上而其典型的设计代码修改可在不到一天的时间里就可完成。此外,它还可以在硬件仿真系统的交互式调试环境下快速调试问题。这是通过将独有的硬件仿真器中基于定制芯片的硬件架构(Mentor Graphics称之为“片上仿真器”)与用于实现映射过程自动化并为有效调试提供完整的交互式设计访问的仿真系统的软件相结合得以实现的。

在过去,我们的任务仅仅是将简装原型系统提供给软件开发人员。即便如此,原型系统的完成通常也是在数月之后。而现如今,公司可以提早共享一个完整的硬件仿真系统。然而,真正的好处在于,公司能够为客户提供经过完整软件基础包验证过的更加优质的工程样品。多年以来,帮助客户加快产品上市步伐所带来的经济影响已被多项研究得以证实。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)