随着雷达技术的进一步发展,对雷达信号处理的要求越来越高,在实时信号处理过程中有大量数据需要存储,由于FPGA本身的存储器容量非常小,根本满足不了雷达信号处理过程中的需求,为解决这一问题,通过查询资料,引入SDRAM和FLASH作为FPGA的外部存储器。SDRAM存储器以其快速、方便和价格相对便宜,因而,常被用在雷达信号实时处理上。选择SDRAM而没有SRAM是因为SRAM价格太贵,SDRAM相对便宜。没有选择DDR SDRAM的原因是因为在实际的雷达信号处理中并不需要那么高burst率,SDRAM足以满足实际需求。SDRAM主要作用:在MTI处理时作为周期延迟器件、动态杂波图的存储和数据暂存等功能。虽然SDRAM有存储容量大、价格相对便宜等优点,但是其断电所有数据丢失的缺点,使其仅在FPGA外部连接SDRAM作为外部存储器件显然是不能满足设计需求的,因此,在设计过程中考虑到FLASH存储。在设计中用FLASH存储一些断电不能丢失的数据,如:脉冲压缩处理时的匹配滤波器系数、MTI处理时杂波加权系数、CFAR处理时的对数表以及一些函数求值等。

1 存储电路设计

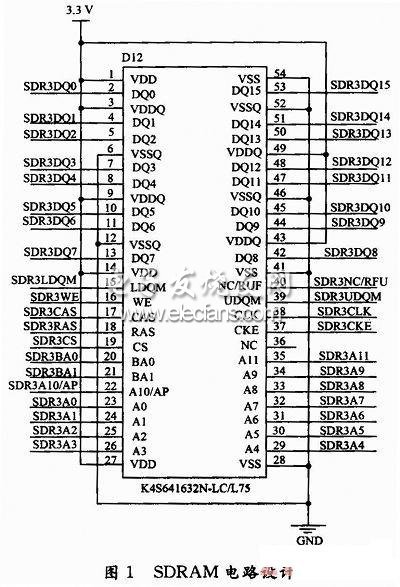

1.1 SDRAM存储电路设计

SDRAM与FPGA的连接,要把FPGA的普通I/O与SDRAM的除电源、NC和接地管脚之外管脚连接起来即可,所有的控制与工作时序都是由FPGA提供,由于管脚太多,采取了网络标号连接,其电路原理图如图1所示。由于篇幅关系,只给出了部分电路图。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)