频率特性是一个系统(或元件)对不同频率输入信号的响应特性,是一个网络最重要的特性之一。幅频特性和相频特性综合称为频率特性。测量频率的方法有点频法和扫频法。传统的模拟式扫频仪价格昂贵、体积庞大,不能直接得到相频特性,给使用带来诸多不便。为此,设计了数字扫频式频率特性测试仪。

1 方案论证与选择

1.1 方案的选择

1.1.1 信号发生模块

方案1:采用模拟分立元件或单片压控函数发生器。可同时产生正弦波、方波、三角波,但由于元件分散性太大,产生的频率稳定度较差、精度低、波形差,不能实现任意波形输出。

方案2:采用传统的直接频率合成器。这种方法能实现快速频率变换,具有低相位噪声以及所有方法中最高的工作频率。但由于采用大量的倍频、分频、混频和滤波环节,导致直接频率合成的结构复杂,并且它也无法实现任意波形输出。

方案3:采用锁相式频率合成器。锁相式频率合成是将一个高稳定度和高精度的标准频率经过加减乘除的运算产生同样稳定度和精确度的大量离散频率的技术,它在一定程度上解决了既要频率稳定精确,又要频率在较大范围可变的矛盾。但由于锁相环本身是一个惰性环节,锁定时间长,故频率转换时间长,频率受限。更重要的弱点是,不能实现任意波形的功能。

方案4:采用直接数字频率合成器(DDFS)。DDFS技术以Nyquist时域采样定理为基础,在时域中进行频率合成,它可以快速改变频率,并且通过更换波形数据可以实现任意波形功能。DDFS相对带宽高,输出相位连续,频率、相位和幅度均可以实现程控。充分利用FPGA内部资源,在其内设置所有逻辑电路实现DDS合成,理论上可达MHz,100 kHz的频段要求很容易实现,而且省去大部分硬件,只需D/A转换输出,避免硬件电路的分部影响。

为尽量减轻硬件负担,充分利用数字资源,在满足应用要求的基础上,选择方案4,在FPGA内部实现频率合成。

1.1.2 被测网络

方案1:直接利用阻容双T网络。可以通过改变电容电阻的参数改变中心频率,但其传递函数形式已经固定,带宽大概是中心频率的4倍,Q值固定为0.25,陷波效果较差。

方案2;采用改进双T网络,网络输出经过射级跟随器反馈回网络,可以限制带宽,容易实现应用要求。为此选择方案2。

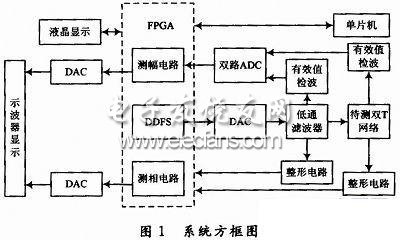

1.2 系统总体实现方框图

系统方框图如图1。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)