比较器结构与设计

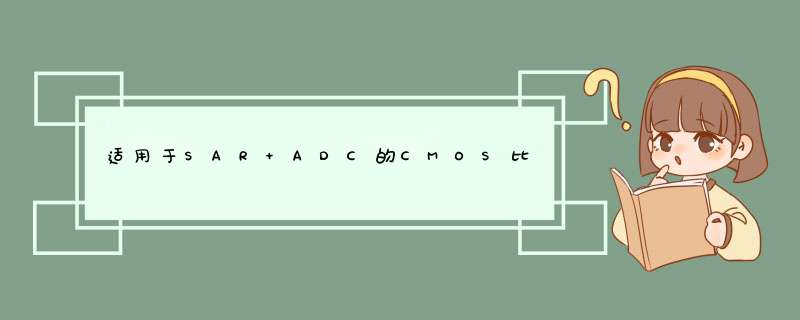

该比较器的结构简化如图1所示。

它由两级结构相同的前置放大器和一级带有复位再生的高速锁存器组成,每一级中都带有一个内置正反馈的设计。前置放大器使输入的变化足够大,并且将其加载到锁存器的输入端,这样获得电路的最佳特性。

前置放大器的设计及优化

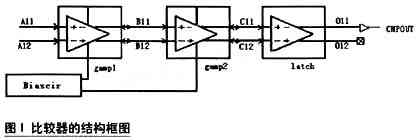

传统的前置放大器结构如图2所示,这种内置正反馈比较器由一个差分输入对,一个伪电流源和一对交叉耦台负载组成,负载连接成差分的模式。M1和M2组成差分输入对,M3、M33、M4、M44组成带有正反馈的负载,以提高电路的增益,这个正反馈单元电路可以通过调整M3、M4和M33、M44管的宽长比(W/L)来形成弱正反馈或强正反馈。

前置放大器电路中的正反馈分析

正反馈是通过连接到M3和M4的源一漏极的并联电压反馈。其比较的工作过程为:差分输入信号加到NMOS对管M1和M2的栅极,假设一端加正电压信号,另一端则为负电压信号;NMOS管M1中流过的电流Ids1开始增大,M2中电流Ids2开始减小,M3和M33栅极电位下降,M4和M44栅极电位上升,M3管中电流Ids3增大,M4管中电流Ids4减小;从而使M4和M44的栅极电位更高,M3和M33栅极电位更低,这个正反馈重复进行直到Ids33随其栅电压减小而增大的速度与Ids4减小的速度相等,以及Ids44随其栅电压增大而减小的速度与Ids3增大的速度相等。

如果忽略M3与M4两个交叉耦合的PMOS管负载的沟道长度调制效应的影响,则交叉耦合负载的作用相当于一个负电阻RX=-2/gm3(其中gm3=gm4)

考虑到M3、M4的沟道长度调制效应的影响,则

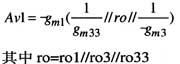

交叉耦合的正反馈负载的负电阻特性补偿了一部分正的输出阻抗,在一定程度上提高了差分输出阻抗,提高了比较器的增益。所以,第一级前置正反馈放大器的增益为:

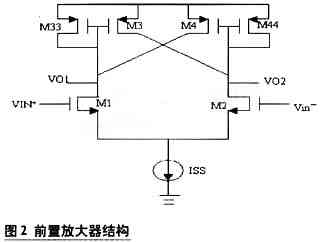

化简得到直流电压增益为:

在C1相同时,时间常数越大,比较器的信号传输时间越长,其转换速度就越低。但同时,比较器的增益却越大,因此导致高增益与高速度的矛盾。

设计优化

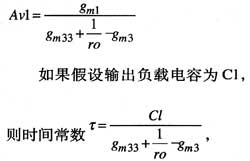

优化后的前置内置正反馈放大器电路结构如图3所示:

RS与 两个相反的时钟信号用来控制比较器的复位,当RS为高时,比较器处于复位状态;RS为低时,比较器开始进行比较。这样通过每次比较前的复位,可以进一步提高比较器的翻转速度。

两个相反的时钟信号用来控制比较器的复位,当RS为高时,比较器处于复位状态;RS为低时,比较器开始进行比较。这样通过每次比较前的复位,可以进一步提高比较器的翻转速度。

为了获得更高的工作速度,在两个输出端之间还有两个钳位二极管,用来控制两个差分输出端的电压差。如果输出电压差值过大,则当本级比较器的输入发生翻转时,两个输出端会由于电压差过大而造成输出端翻转的速度较慢,从而影响输出结果和比较器的性能。所以这两个MOS管可以起到钳位的作用,即限制Vo1和Vo2电压的摆幅,提高比较器的速度。在平衡状态时,通常∣Vo1-Vo2∣

第三级锁存比较器设计

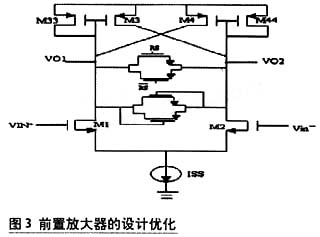

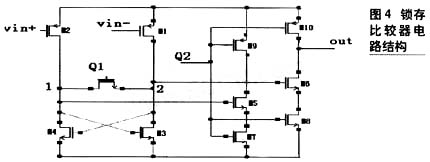

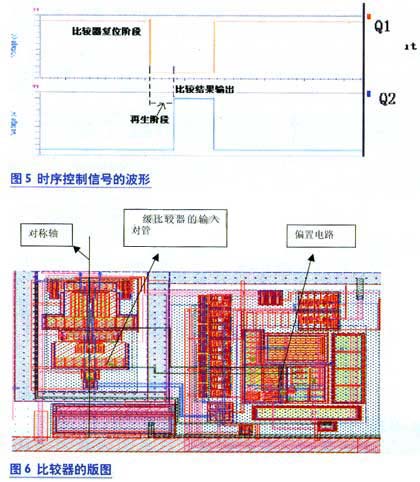

因前置放大器的增益与输入电压的乘积不足以达到输出VOH的要求,所以把放大后的电压再加到锁存器上即可以得到所要求的电压。第三级比较器的结构采用可再生比较器,它也是使用正反馈来实现两个信号的比较。可再生比较器又称为锁存比较器。比较器中两相非交叠时钟控制,确定不同的工作模式,从而实现比较器的复位与输出。其电路的拓扑结构如图4所示。其中两相非交叠时钟Q1和Q2的波形如图5所示。

当时钟Q1为高电平时,比较器处于复位状态。这时节点1和2被置成等电位。接下来是再生阶段,当APX和APV都为低电平时,通过交叉耦合的NMOS管M3和M4的正反馈进行电压再生,使节点1和2的电压一个变高而另一个变低。最后是当Q1为低、Q2为高时,比较的结果通过M5、M6、M7、M8、M9的作用输出,并保存此输出至下一个复位状态。

如图4所示,本设计中的锁存器使用的是NMOS管锁存器。确定锁存器工作时从开始状态到最终状态所需要的时间是很重要的。

当M3和M4管相同时:gm3=gm4=gm,C3=C4=C,R3=R4=R。

比较器要在规定的时间内分辨出两输入信号之间微小的差值,先通过前置预放在T1时间把输入电压放大到Vin,将Vin加到锁存器的输入端,再经过Tp时间达到要求的输出电压,所以总的响应时间T1+Tp必须足够小。而T1与前置放大器的3dB带宽有关,带宽越高则放大信号的时延越小。此设计中两级前置放大器的-3dB带宽约为50MHz,所以T1较小;Tp与锁存器的输入有关,想使Tp越短,其输入Vin就应该越大。前面的两级前置放大器刚好解决这个问题,可以快速建立锁存器的输入,从而提高电路的工作速度。

另外,锁存器较大的输入失调电压和输入管寄生电容的KT/C噪声也会直接影响到比较器的性能,因为这将会限制锁存器的精度。同样通过前两级前置放大器的作用,锁存器的输入失调电压等效到前置放大器的输入端就会变得很小,因此可以较大程度上减小锁存器的输入失调电压和输入MOS管寄生电容的KT/C噪声对比较器性能的影响。

设计结果分析与版图

为了提高增益和工作速度,输入对管的宽长比取值要稍大些。在设计中第一级和第二级前置放大器的偏置电流取值为52μA,其增益分别为14.75和11.8,带宽为40MHz。前置放大器的大带宽有利于减小其响应时间,经过两级放大后,第三级锁存器的输入电压的最小值为Vin_min×14.75×11.8,锁存器较大的输入相应地减小了锁存器的时间常数,使锁存器的输出达到VOH-VOL的时间减小,实现了锁存器的快速锁存。经过仿真,其性能参数如下:电源电压3.3V,输出VOH-VOL=3.3V,最小分辨率0.8mV,功耗<0.6mW,输出动态范围3.3V。

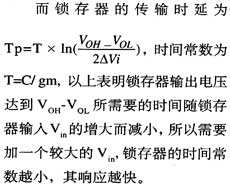

芯片采用了0.18μm的1P6MCMOS设计工艺,在实现高分辨率的同时也能获得较高的速度,模拟结果表明,分辨率可以达到12bit。在版图设计中,为了增强差分管的匹配性,管子和连线都采用全对称的设计结构,版图如图6所示,面积为120μm×130μm。

本设计介绍了一种ADC中常用的比较器,采用了两级前置放大器和一级锁存器组成的三级结构,而且每一级结构内部都带有内置正反馈。本设计采用了简单的结构,以较小的芯片面积,实现了较高的速度和12bit的高精度,可以广泛应用于高速和高精度的ADC中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)