今天与小芯片(Chiplet)相关的成功案例并不多,原因很简单 - 几乎没有为如何连接它们定义的标准接口。

实际上,使用它们的唯一方法是使用专有接口和协议控制接口的两端。唯一的例外是HBM2的定义,它使大量第三方DRAM能够连接到具有高带宽且功耗显着低于芯片到芯片连接的逻辑器件。

小芯片的概念其实很简单,就是硅片级别的重用。设计一个系统级芯片,以前的方法是从不同的IP供应商购买一些IP,软核(代码)或硬核(版图),结合自研的模块,集成为一个SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程。未来,对于某些IP,你可能不需要自己做设计和生产了,而只需要买别人实现好的硅片,然后在一个封装里集成起来,形成一个SiP(System in Package)。所以chiplet也是一种IP,但它是以硅片的形式提供的。

这与设计和制造印刷电路板(PCB)的方式非常相似,只有一切都在一个封装内发生。当所有裸片由同一公司设计和制造并且可以对所有裸片进行修改时,这被称为3D设计。

如果没有标准,市场将无法实现。“你必须拥有芯片和SoC之间连接所必需的行业标准,” eSilicon战略和产品副总裁Hugh Durdan说。“除非有标准,否则你将永远不会在小芯片和人们想要的其他SoC之间拥有必要的互 *** 作性。HBM是芯片到芯片封装内接口的一个很好的例子,并且非常成功。”

这些接口会是什么样子?Netronome的硅架构程序管理主管Bapi Vinnakota说:“它们位于板和模上接口之间。”“它具有板式接口的一些特性,比如必须有传输大量数据的机制,但需要像on-die接口那样具有低延迟。该接口是在板级和裸片级工作的混合。”

选择接口

Marvell于2015年推出了模块化芯片(MoChi)架构,这是一种基于Kandou总线接口的小芯片模型,并且它一直在内部使用该方法用于自己的产品。

“我们遇到的第一个问题是选择接口 - 什么是运行芯片间通信的最佳IP,”Marvell的网络CTO Yaniv Kopelman说。“我们想要在有机基板上运行而不是内插器或者是InFO(台积电的集成扇出)类型的封装,因为我们不想要高成本封装,我们不希望与单个供应商绑定。第二个问题是架构。使用小芯片,您必须在中间划分IP。问题是在哪里切割以及如何开发架构,以便你可以在需要时切换CPU。为此,你必须查看组件的延迟并处理逻辑实现。第三个挑战是将这一切投入生产。在一个演示中构建IP很容易,但从那里到生产有价值的东西还有很长的路要走。“

现在,在专用新接口出现的同时,正在使用通常为其他目的定义的现有接口。CadenceIP Group的高级产品管理集团总监Rishi Chugh 提供了一些例子。“ 芯片互联网论坛(OIF)有针对小芯片和JEDEC委员会的举措。还有像英特尔这样的组织,它拥有高级接口总线(AIB),而英特尔则愿意提供规范。“

新的CEI-112G-XSR(超短距离)项目也旨在实现OIF项目旨在实现光学引擎内部或芯片之间的封装内互连,具有高吞吐量密度和低标准化功率,最大可达50 mm。系统级封装(SIP)设计导致需要在有机封装衬底上的多个芯片之间支持多达50mm的迹线长度。以支持混合技术,特别是用于构建光学引擎。封装基板。

英特尔的AIB是一种芯片到芯片的PHY级标准,它采用模块化方法进行系统设计,并具有芯片级知识产权(IP)模块库。

“AIB使用时钟转发的并行数据传输机制,类似于DDR DRAM接口,”Chugh解释说。“它与工艺和封装技术无关,可以利用英特尔的嵌入式多模互连桥(EMIB)或台积电的CoWoS(芯片对基板的芯片)等技术。”

Intel现在免费提供了AIB接口许可,以实现广泛的小芯片,设计方法或服务提供商,代工厂,封装和系统供应商的生态系统。

Synopsys的 DesignWare IP子系统产品营销总监Mick Posner说:“英特尔有很大的优势,因此,AIB是一个明显的初始赢家。”如果您深入研究AIB或其他建议的接口,它们每个都有不同领域的弱点,无论是性能还是功能。如今所指定的AIB具有性能限制,可以在下一代轻松解决。没有必要提供额外的性能和低延迟。没有明显的赢家。“

每个都有自己的优势。“OIF拥有小芯片的衍生产品,他们称之为XSR超短距离,”Chugh补充道。“这针对封装中的裸片或芯片到芯片互连。因此,该行业正在推进标准化IP。我认为我们今天没有最好的解决方案,因为这是第一次努力,但这是朝着正确方向迈出的一步。标准并不总是最好的,但你必须迈出第一步。“

实现这一目标的好处是大大缩短了上市时间并降低了开发成本。“我们的客户有时可能希望将我们的ASIC解决方案与单个封装中的其他组件结合在一起,然后可以选择将可靠性认证纳入一个封装,而不是单独对所有元件进行认证,” Olivia Slater,Adesto Technologies的运营和物流经理。“根据正在开发的SiP,这可以使认证和最终测试解决方案不那么复杂。”

性能

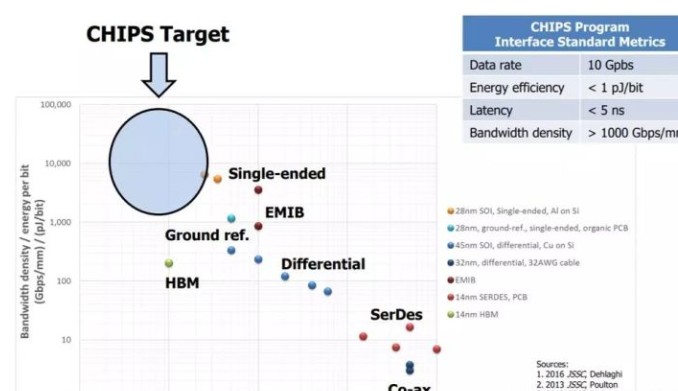

一些组织正在尝试定义这些新的接口,包括DARPA的一个名为通用异构集成和IP重用策略(chip)的项目。DARPA在图1中定义了目标性能空间。

图1.标准接口。

性能需求受到关键物理元素的约束。“当发送数据时,人们寻找的两个标准是功率效率和带宽,”Chugh解释说。“从裸片的边缘开始,你能在不浪费面积的情况下发送的最大数据是多少?” 在裸片的边缘,每毫米我可以传输多少数据。效率是人们将其测量为pJ / bit的功率方面。将每个数据位从一个芯片发送到另一个芯片消耗了多少功率。“

“追踪的数字是品质因数(FOM),”Vinnakota补充道。“只要你在裸片之间连线,就会面临beachfront 问题。你不得不从一个芯片边缘将这些引线从芯片上取下,你可能会烧掉焊盘。FOM是边缘上的线性密度(1 TB / mm),然后移动数据需要多少皮焦耳。“

多层

小芯片接口与任何其他类型的接口一样,往往是多层的,具有物理,链接,传输和其他层,所有这些都旨在确保稳健的通信。ODSA发布了一个图表,显示了可能需要考虑的一些层。

物理层

物理层基本上可以是并行或串行的。“串行的优势在于,您通常最终会使用更少的连线,但成本会增加设计复杂性,”Vinnakota解释道。“并联通常可以在较低的速度下运行。”

但选择比这更复杂。“并行接口(例如AIB)的优点是延迟非常低,功耗和面积非常低 - 所以它从架构的角度来检查所有的盒子,” Durdan说道,“主要缺点是它确实需要硅插入器或类似的芯片封装技术,这会增加成本。“

但选择比这更复杂。“像AIB这样的并行接口的优点是它具有极低的延迟、极低的功耗和区域—所以它从架构的角度检查所有的框,”Durdan说。“主要的缺点是,它确实需要硅插入器或一些类似的封装技术,这增加了很大的成本。串行接口的缺点是,对于某些应用,您不能容忍与SerDes相关的延迟。”

在此应用中,SerDes可能比芯片到芯片解决方案更简单,更快速。“我看到有人试图使用SerDes进行连接,但是它们的体积更小,功耗更低,利用了你只通过非常短的通道进行通信的事实,”Durdan说。“这些是同一封装内的多个芯片,而不是整个电路板或背板。”

AIB是一种并行接口,包括以1或2GHz运行的线束。“AIB有2000条线,几乎强制使用硅插入器或桥接器,”Vinnakota补充道。“如果你是一家小公司,你可能买不起插入器。相反,您可能需要一种基于有机基板的产品,这意味着您需要一种更少连线的技术。内插器可能的线密度比有机基板的线密度高许多倍。“

时钟是两种接口类型之间的主要区别。“通过并行接口,你需要做时钟转发等事情,”Chugh说。“使用SerDes,时钟和数据合并在一起。通过两个设备维持数据的并行性,并且时钟转发保持两个设备之间的时钟驱动器的健全性。它使它成为一种模块化设计,你可以在假设中思考,“如果你有一个裸片并且裸片上有一个数据路径,你就可以在整个数据路径上将裸片切成两块。” 现在你有两个芯片,你试图在同一个封装中将它们拼接在一起,并且这个IP连接了并行数据通路。”

数据路径之外还有其他一些注意事项。“你需要考虑诸如集成自检之类的东西,一个集成的1149边界扫描机制,当它嵌入到封装内时,可以到达芯片,所以它不仅仅是跨越数据传输接口,“Vinnakota警告说。

其他问题也仍不明朗。西门子企业Mentor的Calibre DRC营销总监约翰•弗格森(John Ferguson)表示:“关于在芯片中使用ESD保护的必要性存在一些争议。”“一旦你做到了这一点,它们就会被封装起来,因此没有机会与人体互动。”其中一些会消失,但还有其他的电冲击可能会变得更有问题。这很难说。已经有一些协会对它们进行了调查,大多数都提出了最佳实践。”

PCIe出现在PHY ODSA列表中,因为它已经得到了大量产品的支持。它被认为是一种无需修改就能将带有PCIe接口的芯片转换成芯片的快速方法。

“服务器和高端设备中的大多数芯片已经具有PCIe接口,” ArterisIP营销副总裁Kurt Shuler说。“随着您添加PCIe附带的更多即插即用功能,您会增加堆栈的复杂性。因此,您可以从低级别接口转变为强大的软硬件标准。“

超越PHY

PHY标准的出现是不够的。这不允许真正的功能分离。“在PHY层上已经做了很多工作,用于将小芯片组合在一起,但是要使它们作为单个产品工作,您需要一个体系结构接口。”Vinnakota解释说。“ODSA希望在开放的PHY层之上建立一个开放的接口。”

一致性增加了软件的简单性。Shuler说:“我们的想法是能够设计这些,假设有一个CCIX连接,它将能够连接到任何其他具有CCIX接口的芯片。”“仍然存在一些问题。在设计这两个芯片时,仍然需要在开始时考虑整个系统架构和内存层次结构的上下文。在未来,也许不需要。但是如果你看一下规范,它仍然是一个相当底层的接口。有一些交易正在进行,但你仍然必须对另一个小片如何工作做出很多假设。可以使用不同级别的CCIX连接,当您达到更高级别时,更多的连接会得到处理。梦想是在两个芯片上实现CCIX连接。把他们的身体挂在一个裸片或板上,它只是工作。但今天情况并非如此。”

不过,要想成功,这需要一个系统级的解决方案。Shuler指出:“你永远无法避免有人必须查看整个系统。”“你要做的是获取多个处理元素,每个元素都需要访问内存,你希望它们之间有一个共同的视图。这不仅关系到连接级别,而且关系到芯片的总体架构。这可能是架构指导方针必须被创建——需要连接到芯片内部的什么,才能符合这个即插即用标准。即使是在软件方面,也可能需要一些标准来解释如何与这些类型的芯片进行通信。”

传输信息

在短期内,某些信息可能必须以旧有方式传输。“今天使用IP,您可以获得指定时间和功率的信息,当您谈论裸片时,您将开始拥有更多信息,因为它们处于不同的工艺和不同的金属堆叠和厚度,”Ferguson说。“在某个地方,所有这些细节都需要定义,以便他们知道如何将它们组合在一起。”

可能还需要新的型号。Shuler说:“有一点是不同的,那就是他们想要一个模型,而且可能是在不同的抽象层次上,让其他chiplets的不同部分与他们自己的部分结合起来,能够满足性能需求,处理能力和系统的其他方面。”“有翻转晶体管的观点,还有连接的物理效应。这将不仅仅是一个数据表的共享。这是我的一组模型,你甚至可能需要其中一些用于预售。”

也可能需要新型号。“有一点不同的是,他们需要一个模型,并且可能需要在其他小芯片的不同部分的不同抽象层次上与其自身结合,并能够满足性能要求,处理功率和系统的其他方面,“Shuler说。“存在翻转晶体管的场景,然后还有连接的物理效应。将共享不仅仅是数据表。”

IP供应商可能需要开发新技能。“纯粹的IP玩家在这方面已经有点挣扎,因为他们没有设计芯片或封装的技能,”Durdan说。“芯片间的互连和裸片间的互连与其他IP的最大区别在于,封装是解决方案中不可或缺的一部分。”

结论

鸡和蛋问题正在慢慢解决。标准响应市场,但没有必要的标准,市场就不会发展。

专有接口正在解决如何连接芯片的难题,尽管最终可能是昂贵的解决方案,但是板级标准也提供了一条快速路径。

但即使这些问题没有得到解决,一些公司也永远不会回到单一的解决方案。不可能确切知道什么级别的即插即用是正确的。

责任编辑:pj

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)