随着逻辑设计复杂性的不断增加,在计算机上以软件方式的仿真测试变得更加耗费时间,而不断需要重复进行的硬件系统的测试同样变得更为困难。为了解决这些问题,设计者可以将一种高效的硬件测试手段和传统的系统测试方法相结合来完成,这就是嵌入式逻辑分析仪的使用。它主要用于分析数字系统的检测和故障诊断问题,是数据域测试中一种非常有效的测试方法。它可以随设计文件一并下载于目标芯片中,用以捕捉设计者感兴趣的目标芯片内部信号节点处的信号,而不影响原硬件系统的正常工作。本文介绍Signal Tap II逻辑分析仪的基本用法及其在FPGA中一个典型的应用实例。

1 Signal Tap II基本用法

嵌入式逻辑分析仪Signal Tap II在对系统硬件模块进行监测时,是将测得的样本数据暂存于目标器件的RAM中,然后通过器件的JTAG端口和Byte Blaster II下载线一起将样本数据信息传出并送入计算机进行数据分析。Signal Tap II允许对设计中所有层次模块的信号进行监测,可以使用多时钟驱动,还能通过设置用以确定前后触发信号信息的比例。其使用方法步骤如下:

(1)打开Signal Tap II编辑窗。选择Tool中的Signal Tap Logic Analyzer项,或者选择File中的New项,在New窗口中选择Other Files中的Signal Tap II File,单击OK按钮,即出现图1所示编辑窗。

(2)调入待测信号。注意在调入信号前需给该信号组取名,可通过Instance栏内的Auto Signal Tap_0处单击即可。其次,调入待测信号,在Instance栏的下栏空白处双击即可,如图2所示。在窗口中,点击List,在Nodes Found中就出现所有的待测信号,选择所要测量的信号,点击OK就完成了。在调用信号时,不要过多的调用没有实际意义的信号,这样会导致芯片资源的浪费。

(3)相关参数设置。参数的设置正确与否是使用Signal Tap II的关键。从前面我们已经知道,Signal Tap II将采样的样本存于RAM中,参数设置就是设定采样的特征信息和采样数据样本的大小等参数,采样的特征信息包括采样时钟的采样的速度、触发形式和采样的深度,即采样样本存放于RAM中的点数以及RAM的大小等相关设置。参数设置过程如下,首先,在图1的Signal栏中,点击Clock即可设置采样时钟。采样时钟的快慢影响我们所观察的信号的质量,所以要灵活、合理选择。采样时钟不是越快越好,当我们要观察一些慢速信号或干扰信号的时候,太快就适得其反。其次,设置采样深度。采样深度越深我们观察到的点数就越多,当然是越多越好,但是由于受RAM的大小限制,我们设置的采样深度不可能太深。特别是在采样信号比较多的时候,我们要综合考虑这些因数,设置我们的采样深度,以免发生RAM不够用的情况。再次,根据待测信号的要求,在Buffer AcquisiTIon Mode框的Circulate栏设置采样起始触发位置。最后,设置触发条件,在Trigger中用于选择出发级数,如两级触发,就要在两个触发条件都满足的条件下才能得到触发;在下面的Trigger框中选择触发信号和触发形式,触发形式有上升沿、下降沿等触发供选择,当选择的触发信号满足了所设置的触发形式的时候,就开始采样。

(4)保存。在完成以上的步骤之后,点击保存,出现“Do you want to enable Signal Tap II…”,选择“是”就表示再次编译的时候将Signal Tap II与工程捆绑在一起综合,并通过下载适配器一起下载到FPGA芯片中去。如果选择了否,可以在菜单Assignment中的SetTIng项,Category栏中选择Signal Tap Logic Analyzer,在d出的窗口中的右面,选中Enable Signal Tap Logic Analyzer,单击OK即可。在全部测试完成的时候,应从芯片中去掉Signal Tap II,方法如上所述。

(5)观看结果。保存好了之后,就可以下载到FPGA芯片里面去了。下载方法与普通下载方法一致,这里不在详述。再在图1的JTAG Chain中设置好硬件连接及相关的SOF文件,最后点击Instance右边第二个自动分析按钮就可以启动Signal Tap II来观看样本数据。

2 实例应用

这里设计一个正弦信号发生器,具体说明Signal Tap II的强大功能。

2.1系统硬件

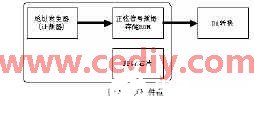

正弦函数信号发生器由地址发生器、数据存储器ROM、D/A三部分组成,根据需要还可以添加移相等其他功能[2],其系统硬件框图如图3所示。

地址发生器实际上是一个计数器,从0开始计数,循环进行。数据存储器ROM的每一个地址对应正弦信号的一个数据,其输入是一个递增的计数值,输出是与其唯一对应。数据存储器ROM 的数字输出经过D/A转换得到了模拟的正弦波形。

2.2系统软件

系统软件采用硬件描述语言VHDL编制,在FPGA中完成软件的编辑、编译,整个系统的VHDL语言描述如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SINGT IS

PORT ( CLK : IN STD_LOGIC; --信号源时钟

DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );--8位波形数据输出

END;

ARCHITECTURE DACC OF SINGT IS

COMPONENT data_rom --调用波形数据存储器LPM_ROM文件:data_rom.vhd声明

PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);--6位地址信号

inclock : IN STD_LOGIC ;--地址锁存时钟

q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );

END COMPONENT;

SIGNAL Q1 : STD_LOGIC_VECTOR (5 DOWNTO 0); --设定内部节点作为地址计数器

BEGIN

PROCESS(CLK ) --LPM_ROM地址发生器进程

BEGIN

IF CLK‘EVENT AND CLK = ’1‘ THEN

Q1《=Q1+1; --Q1作为地址发生器计数器

END IF;

END PROCESS;

u1 : data_rom PORT MAP(address=》Q1, q =》 DOUT,inclock=》CLK);--例化

END;

2.3系统调试

一般地,系统在软硬件设计后,调试工作任务是比较繁重地,如果系统没有达到设计的预期目标,可能出现的问题可能是软件,也可能是硬件。这两个部分无论是软件还是硬件,都是一个非常庞大(对于较大的系统)的工程,每个模块都可能会存在问题,如果不用Signal Tap II来调试,只能检查每一个模块,或根据设计的逻辑检查软件系统。这里我们采用Signal Tap II来调试各个模块。

(1)地址发生器模块检查。通过仿真监测地址发生器的结果是否是一个递增数字量,“是”则该模块正常。

(2)正弦波数据存储ROM模块检查。监测ROM中数据是否为预期的正弦表格中依次的数据,“是”则该模块正常。

可见,用Signal Tap II来调试FPGA优势非常的大,这样可以大大缩短设计人员的测试时间,使得设计尽快投入市场。如果检查全部正确,就说明问题出现的不是软件,而是硬件了。

按照上述Signal Tap II的使用步骤,在编译后的工程中添加STP文件,并对文件进行相关设置,部分参数设置见图4所示。

最后,观察待测信号,如图5所示。如果在待测信号名上右击该信号,在出现的选项中选择Bus Display Format,可以选择以什么数据形式显示采样到的波形,可以有16、10等进制数显示,具体选择根据需要,本例中使用Line Chart来显示正弦波信号,直观、明了,用数字显示就没有这个效果。

3 结论

本文作者提出利用嵌入式逻辑分析仪Signal Tap II为FPGA的内部信号、模块、接点进行测试,这为测试提供了极大的方便,它无需外部器件,方便、经济。另外,在调试FPGA的时候,还可以设置多个嵌入式测量模块等其他功能,这样极大地加快了系统的开发,从而为社会带来巨大的经济效益。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)