1 引言

随着FPGA技术的不断发展和EDA工具软件的完善,在FPGA芯片上实现的各种复杂算法和构建SOPC系统成为研究的热点。在很多科研和教学开展的实验中,都需要为大规模FPGA芯片提供高速的计算机接口以及各种功能部件模块。目前市场上有不少FPGA实验系统,但由于受目标芯片容量、接口、功能部件模块等方面的限制无法满足科研和教学需要。针对研究项目以及对参与项目研究学生培训的需求,我们设计了一套通用的FPGA实验系统,该实验系统以大规模FPGA芯片为核心,带有通用的计算机接口以及丰富的板上功能扩展部件,能较好地满足我们项目研究的需求,并可用于产品开发的原型验证、IC 前端设计验证,IP核验证以及EDA课程实验教学等,同时也可作为高速多通道逻辑分析仪使用。

2 实验系统的设计思想

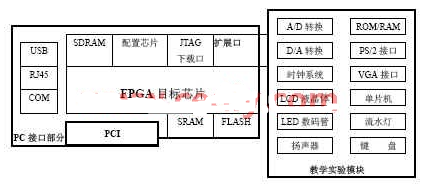

为使实验系统达到通用性的目的,系统上的FPGA芯片应可通过PCI、USB、串行、RJ45(网络)和计算机交换数据,并扩展FLASH、SRAM、SDRAM、JTAG、AS/PS口以及配置芯片等功能部件。为满足学生研究和实验的需要,我们把卡上的FPGA剩余IO引脚扩展到一块教学实验用板中,教学实验板带有A/D、D/A、LCD、数码管、发光二极管、时钟系统、键盘、VGA、PS/2、RAM/ROM、单片机等实验功能模块。

图1:FPGA实验系统的整体框图

3 系统的软硬件设计

本实验系统有多种计算机接口,都采用了成熟的接口芯片,驱动程序由芯片厂家提供,直接调用其上的接口函数实现计算机和实验系统的数据传输。RS232接口设计中用一块LTC1386CS芯片实现电平转换后TXD、RXD信号直接连接到FPGA的IO引脚,USB接口芯片用ISP1581BD,PCI桥接芯片用PLX9054,网络接口芯片用LAN91C111,由于这些接口及相关程序的设计方法有很多共同的地方,因此我们主要介绍PC接口部分中的PCI-FPGA的设计。

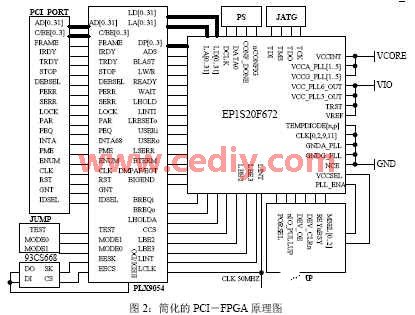

3.1 PCI-FPGA硬件设计

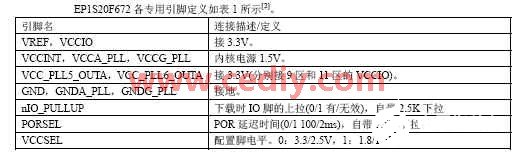

PCI-FPGA部分的电源包括3.3V和1.5V两种电压,1.5V(VCORE)用于EP1S20F672的内核电源(VCCINT),除此之外其它电源都由3.3V(VIO)提供。3.3V电源直接从PCI插槽获取,1.5V电源则通过凌特公司的LT1764AEQ-1.5稳压芯片获得。PCI插槽部分的设计主要是如图2所示把对应信号和9054连接好,另外还需注意把PRSNT1#和PRSNT2中的至少一个接地,目的是让主机认出本PCI设备的存在。工作模式用C模式,配置芯片用的SPROM 93CS66,配置信息参照厂家推荐[1]。

3.2 PCI接口软固件及测试结果

9054的SDK(软件开发套件)提供9054的驱动程序和各种9054的接口访问函数,在此基础上我们开发了几个应用程序接口函数(调用失败返回0,否则返回非0):

int OpenSGLDMAChannel_0(HANDLE hDevice); //打开传输通道

int CloseSGLDMAChannel_0(HANDLE hDevice); //关闭传输通道

int SglDma_Transfer( //用Dma方式传输数据

HANDLE hDevice, //设备号

U8 *sendDmaBuffer, //传输缓冲区首地址

U32 LocalAddress, //局部总线首地址

U32 DataLength, //数据块长度

unsigned int direcTIon //0: PC to Card; 1: Card to Pc );

int Single_ReadWrite( //用单字节方式传输数据

HANDLE hDevice,

U8 *pdata,

int datalength,

DWORD localaddress,

unsigned int direcTIon //0: PC to Card; 1: Card to Pc );

9054局部总线中LHOLDA和READY是输入信号(如图3),其余都为输出。当9054向局部总线写时,LHOLD信号由低转高, LHOLDA应由低转高以响应9054,9054输出ADS为低电平时表示LA上已经出现有效地址,当READY为低电平时,LD上每个周期传输一个数据。当传输到最后一个数据时9054输出BLAST一个周期的低电平,接着LHOLD变为低电平,等LHOLDA也变低则一次DMA传输结束。

我们按以上所述设计并加工了PCI卡,利用FPGA片上的RAM作为输入和输出FIFO,局部总线时钟为50MHz,主机把内存中的数据通过DMA传输方式把数据写入FPGA上的FIFO中。FIFO的深度为1KByte时PCI的传输速度为360Mbps,当FIFO的深度为100Kbytes时,其传输速度达到916Mbps。

4 实验系统的应用

实验系统接口部分研制成功后,主要起以下作用。

4.1 逻辑分析仪

以9054局部总线调试为例,本实验系统(EP1S20F672C7)可作逻辑分析仪使用。首先用VHDL按9054局部总线时序设计好传输数据控制器并综合,接着用QuartusII5.0建立SignalTap文件并设置监测信号及触发条件,编译下载到FPGA中,然后便可进行逻辑分析。以ADS上升沿作为触发条件,BLAST上升沿作为结束条件,对地址线LA[31:0]、数据线LD[31:0]、ADS、LW/R、LHOLD、LHOLDA、READY、BLAST等70路数据DMA传输时进行逻辑分析,其结果如图3所示。

根据综合结果,作为逻辑分析仪,本系统支持最高频率超过220MHz,可对从预留的128个IO口输入的数据进行逻辑分析,存储深度超过1.6Mbits。除可通过QuartusII5.0提供的SignalTap功能对信号分析处理外,也可以把从IO口接收到的数据通过PCI或USB接口传输给主机,然后通过主机编程[3]实现对数据的分析处理。

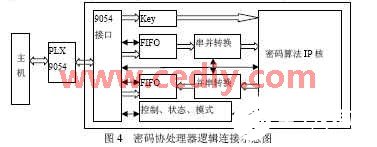

4.2 密码协处理器

本实验系统作为密码算法协处理器使用的逻辑框图如图4所示。以用3DES对一段长消息加密为例,主机分别将控制、模式和密钥等数据送到协处理器的指定寄存器中,接着把明文送到FIFO中,然后待协处理器处理好数据后接收结果。协处理器根据控制、模式等设定,把FIFO中的32位数据转换成分组块,然后启动密码运算模块,处理完一个分组块后再把结果转换并写到FIFO中,并设置状态寄存器,一直到所有数据处理完毕。

由于受到PCI接口传输速率的限制,作为协处理器本实验系统的最大处理速度低于460Mbps(数据进和出)。通过对3DES、AES、SHA1等算法的研究与实现,本实验系统可作为超过400Mbps的协处理器,用于GF(2163)上ECC点乘则可超过3400次/S。

4.3 LEON核的验证

Leon CPU核[4]是公开源代码的32位RISC嵌入式处理器,完全实现了SPARC V8指令体系,可以根据用户的需要对其功能进行剪裁。该处理器由可综合的VHDL代码描述,可在FPGA中实现,并且已经成功流片30次以上。其性能、功耗及配套工具虽比不上MIPS和ARM,但0.85MIPS/MHz的处理速度(Dhrystone2.1测试平台),对嵌入式Linux, eCos, Thumbpod(java), SnapGear等多种嵌入式 *** 作系统的支持,免费获取VHDL源代码与其配套的交叉编译工具、主机调试工具以及嵌入式 *** 作系统是其优势所在。

在我们的实验中Leon2 CPU核使用9830个LE,系统时钟频率达到40MHz以上。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)