引 言

现代科技对系统的可靠性提出了更高的要求,而FPGA技术在电子系统中应用已经非常广泛,因此FPGA易测试性就变得很重要。要获得的FPGA内部信号十分有限、FPGA封装和印刷电路板(PCB)电气噪声,这一切使得设计调试和检验变成设计中最困难的一个流程。另一方面,当前几乎所有的像CPU、DSP、ASIC等高速芯片的总线,除了提供高速并行总线接口外,正迅速向高速串行接口的方向发展,FPGA也不例外。每一条物理链路的速度从600 Mbps到10 Gbps,高速I/O的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员所面临的巨大挑战。这些挑战使设计人员非常容易地将绝大部分设计时间放在调试和检验设计上。

本文就调试FPGA系统时遇到的问题及有助于提高调试效率的方法,针对Altera和Xilinx的FPGA调试提供了最新的方法和工具。

1 FPGA一般设计流程

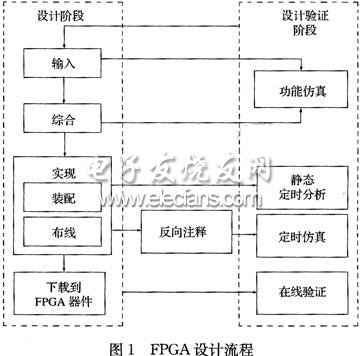

在FPGA系统设计完成前,有2个不同的阶段:设计阶段、调试和检验阶段,如图1所示。设计阶段的主要任务是输入、仿真和实现;调试和检验阶段的主要任务是检验设计,校正发现的错误。

1.1 设计阶段

在这一阶段不仅要设计,而且要使用仿真工具开始调试。实践证明,正确使用仿真为找到和校正设计错误提供了一条有效的途径。但是,不应依赖仿真作为调试FPGA设计的唯一工具。

在设计阶段,还需要提前考虑调试和检验阶段,规划怎样在线快速调试FPGA,这可以定义整体调试方法,帮助识别要求的任何测试测量工具,确定选择的调试方法对电路板设计带来的影响。针对可能选用的FPGA存在的高速总线,除了考虑逻辑时序的测试和验证外,还应该充分考虑后面可能面临的信号完整性测试和分析难题。

1.2 调试和检验阶段

在调试阶段,必须找到仿真没有找到的棘手问题。怎样以省时省力的方式完成这一工作是一个挑战。本文将研究如何选择正确的FPGA调试方法及如何有效地利用新方法的处理能力,这些新方法可以只使用少量的FPGA针脚查看许多内部FPGA信号。如果使用得当,可以突破最棘手的FPGA调试问题。

1.3 FPGA调试方法

在设计阶段需要作出的关键选择是使用哪种FPGA调试方法。在理想情况下,设计者希望有一种方法,这种方法可以移植到所有FPGA设计中,能够洞察FPGA内部运行和系统运行过程,为确定和分析棘手的问题提供相应的处理能力。

基本在线FPGA调试方法有2种:使用嵌入式逻辑分析仪以及使用外部逻辑分析仪。选择使用何种方法取决于项目的调试需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)