引言

时间延时积分电荷耦合器件 (TIme Delay and IntegraTIon Charge Coupled Devices) (TDICCD)是近几年发展起来的一种新型光电传感器。主要应用在低照度条件下,对低照度目标有很高的灵敏度。TDICCD通过多级积分来延长积分时间,从而提高器件的灵敏度和信噪比。

TDICCD成像系统一般由CCD感光芯片,驱动时序发生器,逻辑控制单元,信号处理单元以及外部光学成像系统等部分组成,其中关键是驱动信号的产生。CCD芯片的转换效率、信噪比等光电转换特性只有在合适的时序脉冲驱动下,才能达到器件工艺所规定的最佳值而输出稳定可靠的视频信号。驱动时序发生器性能的优劣直接决定了CCD相机的品质参数。

本文分析了IT-EC-6144型TDICCD图像传感器芯片的工作过程和对驱动时序的要求,在此基础上设计出合理的时序控制方案.由于目前CCD应用向高速、小型化、智能化方向发展。可编程逻辑器件(FPGA)以其高集成度、高速度、高可靠性、开发周期短,可满足这些需要,另外可编程逻辑器件可以通过软件编程对其硬件的结构和工作方式进行重构,从而使得硬件的设计如同软件设计那样方便快捷,因此,选用可编程逻辑器件(FPGA)作为硬件设计平台,结合VHDL语言对时序驱动电路进行硬 件描述,采用QuartusⅡ软件对所设计的时序发生器成功的进行了系统仿真。

1 、TDICCD驱动时序发生器原理

1.1 工作原理

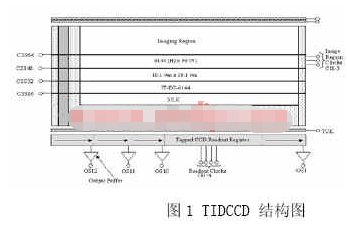

TDICCD是一种具有面阵结构,线阵输出的新型CCD,较普通的线阵CCD而言,它具有多重级数延时积分的功能。从其结构来看,多个线阵平行排列,像元在线阵方向和级数方向呈矩形排列,它的列数是一行的像元数,行数为延迟积分的级数(M),像元分布示意图如图1所示。

图1中TDICCD的电荷积累方向是沿Y向进行的,其推扫级数自下至上为第1级至第96级。在成像过程中,随着相机(或景物)的运动,TDICCD从第96级至第1级依次感光,电荷从第96级至第一级逐级积累。最终,经过多重延

时积分积累起来的电荷包(成像数据信息)转移到CCD水平读出寄存器上,按普通线阵CCD器件的输出方式进行读出。因此TDICCD输出信号的幅度是M个像元积分电荷的累加,输出幅度扩大M倍,而噪声只增加![]() 倍,因此信噪比提高

倍,因此信噪比提高 ![]() 倍。

倍。

IT-EC-6144型TDICCD是加拿大DALSA公司生产的一种高灵敏度、低噪声和宽动态范围的线阵CCD器件,具有较高的灵敏度和很低的暗电流噪声。该CCD主要应用在低照度的条件下,对低照度目标有很高的灵敏度。

1.2 驱动时序分析

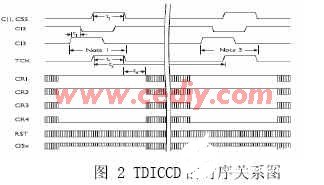

TDICCD比一般线阵CCD具有更优越的性能,但它的控制和驱动也比一般线阵CCD复杂。它共有9个时钟驱动信号和4个积分级数选择端,并对时钟波形和时钟之间的相对关系要求十分严格。

时序关系如图2所示,由图可知,TDICCD的一个工作周期分为两个阶段:光积分阶段和电荷转移阶段。在光积分阶段,存储栅和模拟移位寄存器隔离,不发生电荷转移,而是分别工作,存储栅进行光积分,采集到的光信号在三相移位时钟(CI1-CI3)脉冲驱动下将光敏区的图象信号推至下一行用于积分(且必须遵循:在任一瞬时,至少有一相处于高电平状态,且至少也有一相处于低电平状态)。复位信号清除移位寄存器中的残余电荷。在电荷转移阶段,存储栅和模拟移位寄存器之间导通,在转移时钟TCK(当TCK和CR1处于高电平时,电荷从光敏区的最后一行转移到输出寄存器的CR1相。TCK高电平时间不能和CR1高电平时间重合两次,CI1时钟信号在TCK和CR1为高电平至少100ns之后才能变低。TCK的下降沿出现在CR1下降沿之前至少100ns,CI1下降沿之后至少1s)的作用下将光敏区的电荷转移到输出寄存器,在读出时钟CR1-4(要求CR1的下降沿与CR3的上升沿,CR2的下降沿和CR4的上升沿,有50%的重合才能保证图像电荷包的输出)的驱动下,将输出寄存器中的电荷包推至输出结构进行读出。

CSSX级数选择端,该IT-EC-6144型TDICCD具有级数选择功能,为了适应不同的光照条件,通过设置CSSX,可以进行16、32、48、64和96级的级数选择。根据所选的级数,把相应的CSSX管脚接到-10V,其他未用CSSX管脚接CI1即可。

为了保证CCD能够正常工作以及得到高质量的图像,必须严格控制时钟波形和时钟之间的相对关系[3]。

2、 TDICCD驱动时序的FPGA实现

2.1现场可编程门阵列(FPGA)

采用现场可编程门阵列(FPGA),其包括输入输出块,可构造逻辑块和可编程连线资源三种结构,其集成度远远高于PAL等传统的PLD器件,并在速度上有一定的优势,成为高频领域应用的首选器件。

2.2 CCD驱动时序的VHDL描述

系统采用Altera公司开发的QuartusⅡ软件平台与仿真环境,利用VHDL语言(HDL,Hardware DescripTIon Language),以自上至下的方式,设计出产生时序所需的组合逻辑电路,然后编译,加载到可编程器件中,实现硬件设计的软件化。

设计复杂的CCD驱动时序器,关键是如何用VHDL语言来描述CCD的驱动时序关系。首先定义时序驱动器的输入输出端:13个输入段,即11个行频输入端,通过设置各个端口的高低电平,控制行频周期最大是时钟周期的2048倍;时钟输入;复位信号;13个输出信号,即9个时钟驱动信号和4个积分级数选择端。

由以上分析,总体设计思想是将驱动时序分成3个模块,分别是FENPIN模块,COUNT模块和DELAY模块。FENPIN模块实现将输入时钟进行4分频和6分频,它的输出作为COUNT模块的输入。COUNT模块实际是计数模块,它用FENPIN模块的输出作为时钟输入,在时钟的上升沿计数,计数的前5个周期内,输出为高电平,在计其它数时输出为低电平,在计完2048个数时时钟归0,而后循环计数。然后再将这两个模块的输出进行一些逻辑运算,就可以得到所需要的驱动时序。

由于各时钟波形之间的相对关系要求非常严格,所以需要DELAY模块需要将各时序的相位关系进行调节,以满足实际需要.

2.3 CCD驱动时序的系统仿真

使用QuartusⅡ软件对驱动时序进行仿真,时序电路中FPGA除了提供CCD所需的驱动时序外,还提供视频处理电路所需的时序,并仍然保留了部分的引脚和功能模块,以备今后时序电路的进一步更改和增加新功能的需要。

2.4 电平转换

FPGA电路设计的功能仿真波形如图3,图4所示。FPGA输出的信号并不能直接驱动TDICCD, 因此在时序电路与CCD传感器之间需增加脉冲驱动电路,将信号电压值转换成所需电压值,满足芯片需要。设计中采用专用电平转换模块EL7212进行电平转换。

由于CI1波形,TCK波形与CSSr 波形相同(偏置不同),所以用FPGA产生时序时只需产生一个波形即可。通过脉冲驱动电路,将CI1信号转换为满足要求的CI1、TCK和CSS波形。经过脉冲驱动电路以后的时序信号输出波形与图2的时序波形相吻合,达到了预期的结果。

3、 结论

在分析TDICCD图象传感器驱动时序的基础上,使用FPGA设计出满足实际要求的TDICCD驱动时序,该时序驱动器已经应用于国家某重大项目中,满足系统需要,工作稳定可靠,且性能良好。

另外,本文提出的TDICCD驱动电路,不仅可以达到几十MHz的驱动频率,而且编程方便,硬件电路简单,根据实际需要只要更换晶振并且适当修改程序就能实现特定目的,具有较强的灵活性。通过仿真及实验验证,证明本方法切实可行,该时序不仅适用于TDICCD驱动电路的设计。对于其他需要多种逻辑信号的场合也同样适用。

本文作者创新点:使用新型的CCD图象传感器-TDICCD,该TDICCD具有级数选择功能,可以使系统于不同的光照条件,从而具有好的灵敏度和信噪比。设计出可选级数的驱动时序发生器。很好的应用到新型TDICCD图象传感器中,并且性能良好。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)