正交幅度调制是频率利用率很高的一种调制技术。与其他调制技术相比,具有能充分利用带宽、抗噪声能力强等优点,在移动通信、有线电视传输和ADSL中均有广泛应用。它的载波信号的FPGA实现一般采用DDS(直接数字频率合成)技术,即在两块ROM查找表中分别放置一对正交信号。通过这种方法虽然可以输出一组完全正交的载波信号,但它主要用于精度要求不是很高的场合,如果精度要求高,查找表就很大,相应的存储器容量也要很大,使系统的运行速度受到限制,不适合现代通信系统的发展。本文基于CORDIC(Coordinate RotaTIon Digital Computer)算法,研究正交幅度调制解调器的FPGA实现方法。该方法不仅能够节省大量的FPGA逻辑资源,而且能很好地兼顾速度、精度、简单及高效等各个方面。

1 正交幅度调制解调器工作原理

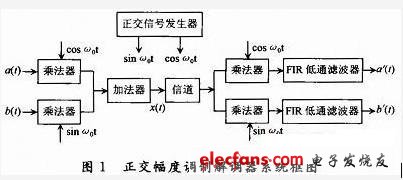

正交幅度调制解调器系统框图如图1所示。其中,a(t)和b(t)为两路相互独立的待传送基带信号,正交信号发生器输出两路互为正交的正弦载波信号,经过两个乘法器可以获得互为正交的平衡调幅波,即不带载频的双边带调幅波。假设乘法器的乘法系数为1,则经过加法器产生的调制信号为:

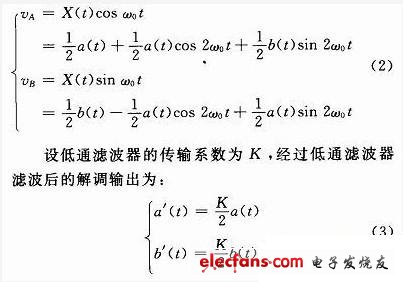

对调制信号X(t)进行解调,采用了正交同步解调方法。已调正交调幅信号X(t)分别与正交信号发生器产生的余弦信号和正弦信号相乘后产生两路输出信号:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)